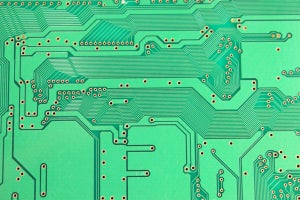

以上が概要であるが、今回のHot Chipsでは、キャッシュの構造やリングインタコネクトについて技術的な発表が行われた。次の図のように、LLCのキャッシュラインは従来と同じ64バイトサイズであり、4コア全体で16Wayのキャッシュを構成している。つまり、LLCは物理的には各コアとペアになっているが論理的には一体のキャッシュとなっており、各コアがアクセスしたメモリデータはアドレスに従って4つのLLCに振り分けられ、自分のペアとなっているLLCだけに入るわけではない。

このコアとLLCをつなぐリングバスは、32バイト幅のデータリングとリクエストリング、アクナリッジリング、スヌープリングという4つのリングから構成されている。これらのリングはパイプライン構造になっており、バケツリレー的に各接続ポイント(リングストップ)間のデータ転送ができるので、リング全体として単位時間に運べるデータ量はリングストップの数に比例して増加する。従って、コア数を増やしてもコアあたりバンド幅が減少するわけではない。しかし、リングストップの数が増えるとデータのアクセス時間は長くなるし、1つのデータが伝送される区間数が増えてバンド幅を多く消費する。このため、時計方向と半時計方向の伝送を行う2つのリングがあり、どちらか近い方を使うことになっている。

このようにリングを回る方向も変わるし、メモリをアクセスするコアとデータが格納されるLLCの位置もアドレスによって変わってしまうので、各コアのメモリアクセス要求がLLCに届く時間が変わってしまう。このため、リングはメモリアクセスの順序を保証しない。これは多くのメモリアクセスが並列に実行でき、性能が上がることになるが、一方、アクセス順序に依存するプログラムは正しく動かなくなる場合が出てくる。このため、Sandy Bridgeではアクセス要求を出すリングストップを持つコアやSystem Agentなどがメモリアクセス順序を確保するという責任を持つという設計になっている。

キャッシュコヒーレンシの維持はMESI方式で、アクセス要求を出すソース側がスヌープ要求を他の全てのプロセサコアに送るという基本方式は前世代から変わっていない。

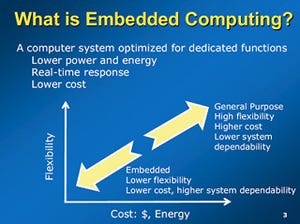

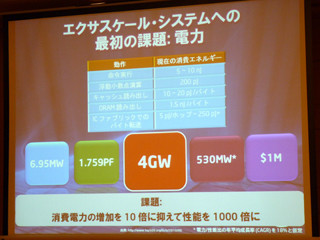

最近ではプロセサの消費電力が最大の問題であり、省電力設計が重要になってきている。

Sandy Bridgeでは、System Agent、コアとLLC、そしてグラフィックス部と3種類の電源系があり、それぞれ独立の電源電圧とクロックで動作させられるようになっている。なお、リングはSystem Agentとグラフィックスの部分にも伸びているが、リング自体は全てコアと同じ電源、クロックで動作するようになっている。このように別々の電源を使うのは、それぞれの部分がビジーな場合は電源、クロックを高くして性能を上げ、一方、暇な場合は電源、クロックを下げて省電力を実現するためである。

本当は、コアごとに動作状態が違い最適の電源電圧は異なるのであるが、プリント基板上に多数のDC-DCコンバータを持ち、パッケージを経由して各コアに接続することは難しいので、全部のコアを1つの電源にまとめている。しかし、あまりビジーでない場合はクロックを下げたり、完全にアイドルの場合は電源スイッチを切ったりすることにより、ある程度の省電力が出来る構造となっている。

そして、チップに内蔵されたPCU(Power Control Unit)が電力の使用状況を監視して、コア側とグラフィック側の電源電圧やクロックを調整して電力配分を最適化する。