L2 D-Cache Line Size Determination(グラフ101~104)

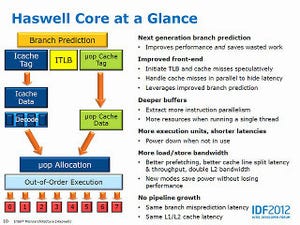

Cache Line Sizeそのものは64Byteとこちらに明示されているので、今更測定の必要は無いのだが、64Byteを超えてアクセスした場合にLatencyがどう変わるのか、を比較するためにこちらも示してみた。ちなみにL2とあるからにはL1 D-Cache Line Size Determinationというテストもあるのだが、こちらはどんなアクセスパターンでも常に一定だったので、結果の分析は省いている。

さて、まずグラフ101がForwardである。64Byteまでは32cycle程度で安定している(1~2Byteのときに大きなピークがあるのは、128bit幅のLoad/Storeユニットに対してあまりにデータ量が少ないため、オーバーヘッドが大きく出たものと思われる)が、その先はちょっと暴れている。

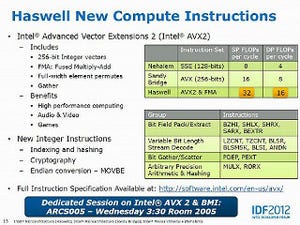

この暴れ方が、Backward(グラフ102)ではまた傾向が変わっているが、ForwardではHaswellとIvy Bridgeが概ね同等だったのが、BackwardではややHaswellのLatencyが大きめになっている。

Random(グラフ103)ではこれがより顕著になっており、ピークはそれほど差が無いが、ピーク間のLatencyはHaswellの方が明らかに多い(64Bytes毎にピークがあるのは、Line SizeのBoundaryに引っかかっているかどうかの判定が余分に掛かるためではないかと想像する)。

更に顕著なのはPseudo-Random(グラフ104)で、どうしてHaswellはこんな傾向になるのかさっぱり理解できなかったりする。ただこのあたりの振る舞いを見るに、結構このあたりにも手が入っていることが想像される。