I-ROB(グラフ19~22)

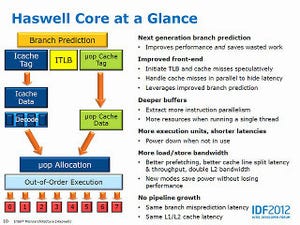

ではROB(Re-Order Buffer)は? というと、Forward/Backward(グラフ19・20)ではご覧の通り殆ど差は見られない。細かいことを言えば、最初の40pointまでの平均を見てみるとIvy BridgeはForward/Backwardともに大きな差が無い(どちらも平均16.1cycle)のに対し、HaswellではForwardが15.5cycle、Backwardが16.5cycleとやや差がついており、少し構成が変わったようだ。ただ、もともとHaswellのバックエンドに関してはバッファ類をかなり強化しており、ROBも当然増えていると考えられるので、多少アクセス時のLatencyが変わるのは当然だろう。

もっとドラスティックに変わっているのがRandom(グラフ21)で、Ivy Bridgeが168程度、Haswellが192あたりでBuffer Overflowするのがわかるが、この数字はHaswellの"Out-of-Order Windows"のものがそのまま示されている。このあたりは数字が明確に確認できたわけだ。ただその代償として、平均して5cycleほどLatencyが増えているが、210cycle弱が210cycle強に増えただけだから、これは許容範囲内だろう。同様にPseudo-Random(グラフ22)でもLatencyの増加が確認できる。Forward/Backwardではここまでの差はないあたり、Pipelineを経由するトータルのLatencyというよりは、ROBのサイズが大きくなった分、アクセスに若干Latencyが増えたということだろう。このあたりの損得勘定は微妙だが、Intelとしては多少Latencyが増えてもROBのサイズを大きくするほうが有利、と判断したものと思われる。