ハードウェアレベルでCPUとの連係を高める次世代GPU

GPUコンピューティング環境を普及させるためには、GPUそのものの進化も不可欠となる。スコット氏は「2012年には次世代GPUの"Kepler"(ケプラー:開発コードネーム)を投入する。その消費電力あたりのパフォーマンスは現行世代の2倍近くにまで向上する」とアピールする。さらに同氏は、"Kepler"とその次の世代のGPUとなる"Maxwell"(マックスウェル)のデザインゴールについても言及し、

- 消費電力あたりのパフォーマンスを向上させ続ける

- GPUコンピューティングの応用範囲の拡大

- より緊密なGPUとCPUの連係(または統合)の実現

- プログラマビリティの拡張

の4つを挙げ、同社の最新GPUアーキテクチャロードマップを公開した。

|

|

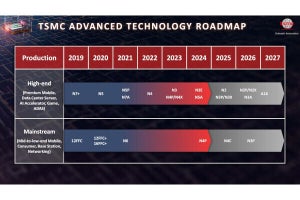

2010年のHPC関連技術カンファレンス「SC10」で公開されたNVIDIAのEchelon計画。128個のSM(Steaming Multiprocessor)とLatency Processorsと呼ぶ8つのARM CPUコアを統合する計画だ |

同社が公開した最新ロードマップで注目すべきは、縦軸のGPUパフォーマンスが"倍精度"かつ"持続的性能"であることだ。GPUのピーク演算性能は演算ユニットの大幅な変更がない限り、コア数と動作クロックに大きく左右される。しかし、持続的性能ということになれば話は別だ。現在、GPUコンピューティングのボトルネックになっているのは、CPU-GPU間のデータ共有にかかるレイテンシ(遅延時間)の大きさが、GPUの待ち時間を大きくし、本来GPUが持っている演算性能を引き出せない状態を生じさせる。NVIDIAが自社開発のARMコア"Project Denver"(プロジェクト・デンバー)を立ち上げたのも、CPUコアをGPUに内蔵することで、よりシームレスなデータ共有を実現することを目指しているためであり、すでにエクサスケールHPC向けプロセッサとして、ARMコアとGPUコアを統合した"Echelon"(エシュロン)を開発していることを明らかにしている。スコット氏は"Kepler"または"Maxwell"でCPUとの連係をさらに高めていくとしており、CPUコアを内蔵しないまでも、GPU側で仮想メモリをサポートするなどしてメインメモリへのアクセスを効率よくするなどのアーキテクチャ拡張を行なう可能性は高い。