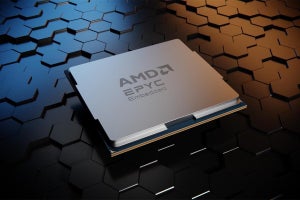

AMDの「Data Center and AI Technology Premiere」の速報(というか事前説明会)の資料によるレポートは既にお届けしたが、ここからは実際のイベントで公開された情報を元に、もう少し細かい内容をお届けしたい。まずは第4世代EPYCの新製品である「Bergamo」と「Genoa-X」の詳細である。

3種類の派生がある第4世代EPYC

そもそも第4世代EPYCは昨年発表された「Genoa」が基本になるが、これに「Genoa-X/Bergamo/Siena」の派生型がある事が昨年6月に行われたFinancial Analyst Dayで既に発表されている。このうちSienaについては今回はまだ未公表(今年後半に発表とだけ説明されている)ということで、今回はBergamoとGenoa-Xの詳細がメインである。

-

Photo01:ただ昨年6月の発表ではSienaはTelco向けとされていたのが、今回Telco/Edge向けとなっている。そこで「ひょっとしてSienaはEPYC Embedded向けにも投入されるのか?」と水を向けてみたが返事は「未発表の製品の詳細は公開できない」の塩対応

さてGenoaとGenoa-X、Bergamoの特徴をまとめたのがこちら(Photo02)。

-

Photo02:Core IPCは3製品とも全く同一である。Genoa-XはPower Efficiencyがやや向上しているのは大容量L3の効果で効率が上がっているためだろう。ただ動作周波数は微妙にGenoaより落ちているのだが……

グレーはGenoaで、これは汎用ということで5つの指標について全て100%と換算した場合、

- Genoa-X(オレンジ):キャッシュ容量を大幅に増加させている。ただしそれ以外は概ねGenoaと同じ

- Bergamo(水色):コア密度と性能/消費電力比を大幅に向上させている一方、動作周波数はやや控えめで、またキャッシュ容量が結構減っている

という違いがある。

要するに以前も書いたが、BergamoはL3を大幅に削り、その分実装密度を上げた製品である。一方でGenoa-XはGenoaの全ダイに3D V-Cacheを搭載してL3を増量した製品という訳だ。

最大128コアを搭載するZen 4CことBergamo

さてまずはこちら。Zen 4cの特徴をまとめたのがこれ(Photo03)。

要するにL3が半減している訳だ。逆に言えばL3以外のCoreそのものはGenoaと全く一緒である。ただし論理的には全く一緒ながら物理的には再設計されており、実際Core+L2のサイズは35%縮小されている(Photo04)。

これに加えL3の容量も半減している格好だ。ちなみに当然L3もPPAも消費電力/エリアサイズに最適化しているとは思うのだが、元々L3は速度優先にされるケースは少ないので、ここではあまり差がないかもしれない。またGenoaの方は3D V-Cacheの搭載を前提に、L3には積層用のTSVエリアが設けられているが、BergamoのL3には「容量拡張用のオプションは一切考えられておらず、TSVのエリアも存在しない」との事。このため、L3のエリアサイズも半分をちょっと切った程度になるかと思われる。

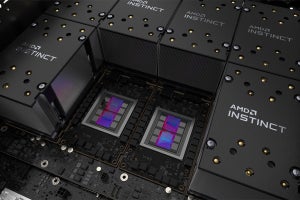

さてその縮小されたCore 128個を、8つのダイに収める格好になる(Photo05,06)。

つまりダイあたり16 Coreになる計算だが、CCXそのものは1つあたり8 Coreで変わらない。つまり1つのダイに2 CCXが搭載される格好だ。つまり初代のZenとかZen 2などと同じ構成である。こうなると気になるのは、「同じダイに搭載された2つのCCX同士は直接通信出来るのか、それともcIoD経由での通信になるのか?」だが、これはSam Naffziger氏(SVP, Corporate Fellow and Product Technology Architect)によれば後者との事。まぁこれをいじるのは大変だろうから仕方がないところだ。

逆にcIoDそのものはGenoaのものと完全に同一という話であった。従ってGenoaの8ダイ構成と同じ形で接続される事になる。Genoa世代のcIoDはダイとの接続用のInfinity Fabric(GMI3)が12ch用意され、Narrow(1ch/ダイ)とWide(2ch/ダイ)の2種類の接続が可能である(Wideでの接続例がこちら)。なので、もしBergamoのダイが6つ以下であればWide接続の可能性もあるのだが、発表時のSKUは128コア(8ダイ)ないし112コア(7ダイ相当)とされているため、残念ながらWide接続の可能性はない。

そのBergamoの現時点でのSKU一覧がこちら(Photo07)。

-

Photo07:全モデルL3が256MBとあるので、EPYC 9734もダイそのものは8つで、ただし16 Coreを無効化して112 Core相当にしているものと思われる。多分1 CCXあたり7 Coreにしているとかではないかと思う

面白いのがSMTを無効化したEPYC 9754Sであるが、これは「いくらかの顧客が利用するワークロードの中には、SMTを無効化した方が良いものがある。こうした顧客の為に、最初からSMTを無効化したモデルを用意した」という話であった。

ところでこのSKUを見ると判るが、EPYC 9754/9754SでBase 2.25GHz/Boost 3.1GHz、EPYC 9734だとBase 2.2GHz/Boost 3.0GHzでしかない。96コアのEPYC 9654だとBase 2.4GHz/Boost 3.7GHzという事を考えると、もちろんコア数が増えているのだから動作周波数を抑えないとトータルの消費電力枠に収まらない(定格TDPが360Wなのは同じ)のであるが、特にBoostが結構低めになっているのが判る。ただこの動作周波数の低さが、そのまま効率の改善に繋がっている、という考え方もできる。性能が純粋に「動作周波数×コア」に比例すると考えたとして、消費電力が同じと考えた場合、性能/消費電力比は、

- Baseでの比較:EPYC 9654:EPYC 9754=1:1.222

- Boostでの比較:EPYC 9654:EPYC 9754=1:1.117

という計算になる。悪くても12%、良ければ22%もの性能/消費電力比向上になる、という訳だ。このあたりはコアそのものを低消費電力/高密度に設計し直したことも貢献しているものと思われる。

問題はこのBergamoが利用されるワークロードであるが、AMDの説明によればこうしたものはアプリケーション密度が高く、データの局所性は低く、様々な場所で利用され、何よりも稼働時間がmsオーダーのモノが少なくない、とされる(Photo08)。

-

Photo08:MicroserviceとかAPI ServiceがこのFaaSの典型的な利用例だろう。そこまではいいのだが、TraditionalのRuntimeが∞というのはちょっと言いすぎな気も

確かにこうした用途であれば、キャッシュの少なさはそもそも問題になり難いし、動作周波数をむやみに上げても効率が悪い。なにより動作時間が非常に短い&煩雑にコンテクストスイッチングが発生しそうだから、特性を高効率性に振ってもそれほど効果があるとは思えない。むしろそこそこに動くコアを大量に集積した方が効果が高いだろう。その意味では、本来はIntelのSierra Forestの様に高効率コアを大量に集積する方がより良いソリューションにはなりそうだが、そのために新規にコアを開発するのはAMDにとってはリスクが高い。Zen 4cはそのあたりのバランスを鑑みた上での、現状のAMDにとって最も良いソリューションという事になる。

Photo08は実際にCloudで利用されるアプリケーションを、AmpereのAltra MaxおよびXeon Platinum 8940H/8480+と比較した場合の結果、Photo09はSMTのOn/Offでどう性能が変わるかであるが、EPYC 9754SとEPYC 9754では、確かにトータルのThroughputという意味ではEPYC 9754の方が43%ほど向上しているが、Threadあたりのスループットで言えばSMTを無効化した方が40%ほど向上しており、コア数あたりの性能を取るか、Threadあたりの性能を取るか(これはアプリケーションのライセンスの課金体系によってどちらが得かが変わってくる)でどちらを選ぶかを決める、という事になる。

単に「BIOSでSMTを無効化すれば同じでは?」というのはライセンス料には通用しないため、最初からSMTを無効化したモデルを用意した、という訳だ。

純粋に性能、という意味で言えば競合に比べて2~3倍の数のContainerを稼働させられるとしており(Photo11)、また性能/消費電力比の比較(Photo12)でも、競合製品の2倍以上というのは、TCOを考えれば大きな武器となる。

-

Photo11:これは前提条件として、Kubernetesの元でコンテナあたり25K JOPS/secのSLAを確保した場合の数字である。性能を無視すれば、どの構成でもメモリが許す限りContainerを動かせるのは言うまでもない

ちなみに既にDellのPowerEdgeシリーズが、このBergamoをサポートすることが発表されている(Photo13)。