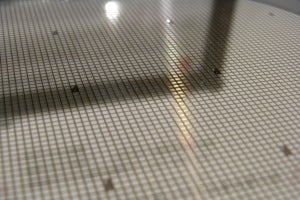

RAMは電圧マージンなどはアナログ的な評価が必要であり、2種類のセルデザインのテストチップを作って評価を行った。また、RAM容量の異なるテストチップも作り、4種類のテストウェハを作って評価を行った。

RAMに関しては次の図のようにstriVe2、striVe4、striVe5、striVe6というテストウェハを作った。striVe2とstriVe4は1KBのメモリで、striVe2はHDcellを使い、striVe4はOSUcellを使っている。striVeとstriVe3ウェハはRAMではなく、Logicセルのテストウェハである。

次に示すテストチップはイメージセンサのテストチップである。その次の図に断面図を示すが、シリコン基板とポリシリコン層のパターンで受光素子を作り、その上の5つのメタル層でイメージングデバイスを構成する電気的な配線を行っていると思われる。前に載せたロジック回路では素子数も少なく、本当に実用的な回路が作れるのか心配という印象をも与えるのであるが、このイメージセンサは実用的な回路が作れるという印象を与える。

次の図はイメージセンサの断面の顕微鏡写真と断面図である。断面図から、イメージセンサは光を感じるシリコン層の上に5層のメタル層がつくられていることが分かる。

次の図はNIST(アメリカ国立標準技術研究所)とのパートナーシップでSKY130 OpenPDKを超低温の4°Kで動作するLSIの作成用に拡張したものの説明である。超伝導を使う量子計算回路が注目を集めているが、多Qubitの量子回路を実用化するには4°Kで動作するマルチプレクサが必要である。しかし、通常のLSIに使われるトランジスタはそのような低温では動作せず、4°Kで動作するトランジスタのSpiceモデルを記述したPDKが必要である。

このように、130nmプロセスでも実用的なロジック回路も作れるし、超電導量子素子のドライバのような特殊なLSIも記述することができる。

シリコンLSIでは2021年12月に4枚目のテストウェハMPW-FOURを作る予定である。このウェハにはReRAMを搭載する予定である。ReRAMは抵抗値を記憶する不揮発性のメモリで、素子が小さいので高密度メモリが作れ、スイッチング速度が速く高速のメモリが作れるというメリットがある。ReRAMを搭載するMPW-FOURウェハは2021年12月に製造予定で、2022年中に4枚製造する予定であるという。

また、アマチュアの衛星通信のトランシーバ、9個のOpenなプロセサコア、ロボット用のアプリケーションプロセサ、暗号通貨マイニング用プロセサ、7個のアナログ/RFトランシーバ、6個のeFPGA、9個のSoCのような実用的な回路の搭載が予定されているという。

-

アマチュアの衛星通信のトランシーバ、9個のOpenなプロセサコア、ロボット用のアプリケーションプロセサ、暗号通貨マイニング用プロセサ、7個のアナログ/RFトランシーバ、6個のeFPGA、9個のSoCの搭載も予定されている

ChipIgnateでは、SKY130 PDKを使って、オープンではなく、プロプライエタリな商用の製品を作っても良い。値段は1品種9,750ドルで、100個のQFP(Quad Flat Package)パッケージに入ったチップか、300個のWCSPパッケージに入ったチップを作ってくれる。また、小規模な量産を行う場合は1000個単位で、1個20ドルで追加購入することもできる。

-

Efabless社は1品種のLSIを9,750ドルで作ってくれる。そして、LSIには100個のQFPパッケージに入ったチップか、300個のWCSPパッケージに入ったチップが付いてくる。また、単価20ドルで1000個のLSIを追加購入して、小規模量産を行うこともできる

OpenMPWプログラムでは16プロジェクトを1枚のウェハに載せ、100チップを貰うと1プロジェクトは5チップ程度の割り当てとなる。一方、ChipIgniteでは9,750ドルで16プロジェクトを搭載できるので、16プロジェクトを集められれば、プロジェクトあたり約610ドルで試作できることになる。

GoogleのMPWプログラムのように無料でLSIを作ってくれるというのは興味深いプロジェクトである。Googleに直接、金銭的なメリットがあるのかどうかは疑問であるが、Googleから見れば気になるような金額ではなく、ハードウェアの設計経験を積んだ若いエンジニアが増えれば、間接的にはメリットがあるのではないかと思う。

ChipIgniteには、通常の10mm2ではなく15mm2の面積を使えるオプションもある。

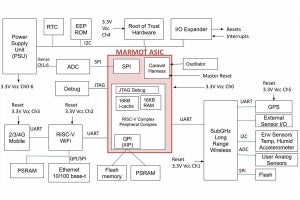

SKY130にはCaravelハーネスが付き、ハーネスにはstd cellやIO cellが含まれている。SKY130チップのサイクルタイム(設計を提出してからパッケージに入ったチップができるまでの期間)は使用するパッケージにも依存するがおおよそ95日である。

なお、2022年には2番目のファウンドリの追加、より性能の高い90nmプロセスの追加や値段の安い180nmプロセスの追加。そして、クラウドベースでの先端のプロセスのPDKの使用を可能にすることなどを考えているという。