プロセスの微細化だけではないTSMCの成長を支える先端技術

7nmの好調さをうたうTSMCだが、次なる微細プロセスの提供もすでに準備を整えつつある。同社は2019年4月に次世代プロセスとなる5nm(N5)のリスク生産を開始し、2020年の上期から本格的な量産に移行する計画を打ち出している。また、N5をより最適化することでパフォーマンスを向上させたN5P(5nm+/N5+)も2021年上期より量産展開することを予定している。

他のファウンドリに先駆け、先端プロセスを提供し、多くの受注を獲得し、さらにその差を広げていくのが同社のビジネス手法と言えるだろう。しかし、その微細化プロセス技術でTSMCに追いつけ、追い越せとばかりに積極的に開発を進め、TSMCに先んじて提供を行おうという企業が出てきた。Samsung Electronicsのファウンドリ事業部(Samsung Foundry)だ。Samsungも7nmプロセスの提供を2018年10月より開始しているほか、2019年4月にはEUV露光装置を活用した5nm FinFETプロセスの開発が完了したことをアナウンス。顧客の要望に応じて6nmプロセスの提供も行っていくことを明らかにしている。また、そのロードマップとしては4nmプロセスならびに3nmプロセスの提供にも意欲を見せており、併せて顧客の獲得に向けた積極的な営業活動も展開しているようだ。

そうしたSamsungの動きに対して四つに組む姿勢を見せるTSMCもN7のシュリンク版ともいえる6nm(N6)のリスク生産を2020年第1四半期に開始することを明らかにしているほか、水面下ではSamsungと同様に3nmプロセスの開発が進められており、2nmの研究についても進めて行くようだ。

N5よりも遅れて提供されることとなる6nm(N6)プロセス。これまでにも同社ではプロセスの最適化により、コスト対比でパフォーマンスの向上を図ってきたことはあるので、別段、無いことはない、という範疇の取り組みではある。表立っては5nmまでのロードマップを公開しているが、アニュアルレポートには3nm以降の開発を進めていることが記載されていたりと、水面下では着実に研究開発が進んでいる模様だ (資料提供:TSMC)

ただ、「イノベーションとしては、新素材や新アーキテクチャの導入、そして基盤となるロジックプロセスに付加されるべきスペシャルなプロセスの拡充も必要になってくる」と、同社ビジネスディベロップメント担当バイスプレジデントのケビン・ジャン氏は語る。実際、10年以上前からTSMCは単なるロジックプロセスのみならず、アナログプロセスやRF、イメージセンサなどのプロセスも提供してきており、継続してその性能向上に努めてきた。

-

ロジックプロセスを中心に、そのロジックプロセスを支えるSpecial Processも用意することで、カスタマのニーズにしっかりと応える取り組みは、10年以上にわたって続けられてきた(Embedded DRAMなども記載されていたときもあった) (資料提供:TSMC)

例えば組み込みフラッシュ技術としては、車載向けフラッシュ混載プロセス技術として28nm品が2020年より本格量産を開始する予定のほか、従来のフラッシュメモリ技術(ESF3)のみならず、ReRAM(RRAM)やMRAMについての研究開発も進められており、いずれも40nmならびに22nmのクオリフィケーションを終えた段階であり、こうした新技術を活用していくことで、20nm以下の組み込みフラッシュプロセスを提供していきたいとしている。

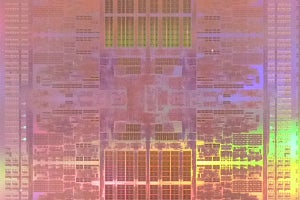

また、近年の同社の成長を牽引してきた1つに3D IC技術がある。Xilinxなどが活用しているメモリとプロセッサなどを1パッケージに集約する2.5D技術「CoWoS(Chip-on-Wafer-on-Substrate)」と、AppleがiPhone 7/7Plusに採用して一躍話題になった一般的にはファンアウト型ウェハレベル・パッケージング(Fan-Out Wafer Level Packaging:FOWLP)と呼ばれる「InFO(Integrated Fan Out)」をこれまでにも提供してきたが、現在はさらに、異なるプロセス技術で製造されたヘテロジニアスなチップを、TSV(Through Silicon Via)やchip-on-waferボンディングプロセスを活用して1パッケージに統合する「SoIC(System-on-Integrated-Chips)」や、ダイ積層技術であるWoW(wafer-on-wafer)といった次世代3D IC技術の開発も進めており、ジャン氏は「技術開発が進めば、将来的には2層ではなく、3層以上のマルチプルレイヤを実現できる可能性もある」と、将来的には1チップで文字通りのSoC(System on Chip)が実現できる可能性を示唆している。

3D IC技術の研究開発も長年にわたって行っており、CoWoS、InFOともに派生系が生まれている(InFO oSはサブストレートの上にSoCを複数搭載することでモバイル向けながら高性能を実現する、InFO MSはHBMとSoCの集積、InFO PoPはInFOパッケージの上に別の半導体パッケージを搭載。このほかにもさまざまな技術が開発されている)。こうした技術の発展系としてSoICやWoWなども開発が進められている

こうした技術の活用先としては、InFOがスマートフォン、CoWoSはHPCなどが中心となってきた。SoICやWoWもHPC関連での活用が想像される。サン氏も「HPC分野は将来的にTSMCの収益の最大化に貢献する市場」と語っており、その期待の高さがうかがえる。ただし、2020年以降、5Gが本格化するスマートフォン市場も盛り返していくことが予想されるため、HPC市場が数年程度で最大のアプリケーション分野になる、ということはないようだ。

なお、同社のグローバル市場の売り上げにおける日本のシェアはこの10年ほどの間、4~6%前後で推移しているが、同社の売り上げ自体は年々増加してきており、それに併せて日本市場の売り上げも拡大してきたといえる。日本法人であるTSMCジャパン代表取締役社長を務める小野寺誠氏によれば、「スマートフォン関連と自動車関連が現在、引き合いが強い」とするほか、「半導体はこれからも確実に伸びていく市場。日本の顧客の中にも長年にわたってお付き合いをさせていただけるような企業もでてきた。今後もより多くの顧客とWin-Winの関係を構築できるように取り組みを進めていきたい」(同)ともしており、最近では大手だけでなく、中堅中小といった企業との取引の増加にも手ごたえを感じているようだ。ファブレス不毛地帯と言われてきた日本で、ファウンドリビジネスを成長させるための地道な取り組みが、実を結んできたと言えそうである。