3種類の構成のFPUの性能を評価

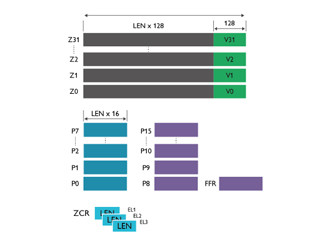

この3種の構成のFPUを、N-bodyの計算とStream Triadの計算で性能を評価している。なお、Arm SVEのベクトルレジスタ数は32で、LEN=4の場合は、128bitのレジスタが128個存在する。しかし、この研究では128bitレジスタの数を96個から192個まで可変して性能や電力を評価している。

次の図の左の棒グラフはN-Bodyの計算時間、右の棒グラフはダイナミックな消費電力を示している。なお、この研究ではリーク電力は無視してダイナミック電力だけをカウントしている。

N-Bodyでの計算時間は、LEN=4では0.33μsの計算時間が、LEN=8では0.17μsで、ほぼ半減している。興味深いのは、LEN=4でもLEN=8でも計算時間は、ベクトルレジスタ数にほとんど影響を受けず、一定であるのに対して、LEN=8 halfだけはレジスタ数が多くなるにしたがって計算時間が短くなっており、96レジスタではLEN=4より44%長い時間が掛かっているが、192レジスタの場合は逆に38%短い計算時間となっている。

LEN=8 halfで96個の128bitレジスタの場合はベクトルレジスタが12個になってしまい、レジスタの入れ替えが増えていることが性能低下の原因ではないかと思われる。しかし、LEN=8のケースでも事情は同じと思われるので、筆者には、なぜ傾向が違うのかは理解できない。

一方、消費電力ではLEN=4とLEN=8はレジスタ数の増加に伴い消費電力が増えているが、LEN=8 halfでは増加ペースが急になっている。これは、縦軸が消費エネルギーではなく消費電力であるので、総消費エネルギーが一定でも、計算時間が短くなると消費電力は増えてしまう。計算時間の短縮が著しいLEN=8 halfの消費電力は、この影響を受けている。

-

N-Bodyでの計算時間と消費電力。LEN=4では0.33μsの計算時間が、LEN=8では0.17μsで、ほぼ半減している。LEN=32 halfでは96レジスタの0.49μsから192レジスタでは0.21μsと大きく変化する。消費電力は、計算時間の短縮の影響で変化している

3種類の構成における消費エネルギー比較

次の図は、縦軸を消費エネルギーとしたもので、レジスタ数の増加に対して消費エネルギーは、ほぼ一定か、わずかに増加するという図になっている。興味深いのは、レジスタ数にかかわりなく、LEN=4に比べてLEN=8とLEN=8 halfのケースでは明確に消費エネルギーが減っている点である。192レジスタの場合、LEN=8 halfはLEN=4より23%少ないエネルギー消費となっている。

次の図は、Triadの計算時間と消費電力のグラフである。Triadは依存性のない積和計算を繰り返す単純なプログラムで、メモリバンド幅を測定するために使われる。一般に、Stream Triadの計算時間はFPUの性能よりもメモリアクセス性能で決まるので、どのFPU構成でも計算時間はほぼ同じである。

消費電力では、レジスタ数が増えるとLEN=8 halfの電力増加が、レジスタ数が少ない領域で著しいが、なぜであろうか? リネームレジスタが少ないことが効いているのであろうか?

次の図はTriadのエネルギー消費のグラフで、計算時間がほぼ一定であるので、消費電力のグラフと同じ傾向の絵になっている。

性能改善と消費電力低減の両立を実現

結論であるが、計算が律速になっているカーネルでは、ベクトル長を長くすることで性能が改善し、同時に消費電力も低減する。N-Bodyの場合、LEN=8 halfはLEN=4に比べて38%のスピードアップを23%少ないエネルギーで処理できている。

一方、メモリ律速のカーネルの実行時間はベクトルレジスタ長には依存しない。また、消費エネルギーもベクトルレジスタ長にはほとんど依存しない。

マルチサイクル演算でベクトルレジスタ長を長くするLEN=8 halfのような方式は、必要なハードウェア量と消費エネルギーの点でバランスの取れた設計になっている。

-

計算律速のカーネルでは、ベクトルレジスタ長を長くすることで性能を改善し、消費電力も減らすことができる。メモリ律速のカーネルではベクトルレジスタ長は性能、電力にほとんど影響しない。LEN=8 halfはハードウェアの増加を抑えて性能を改善するバランスの取れた設計となっている

なお、この研究はPost-Kコンピュータを開発する理研 計算科学研究センター(CCS)で行われたものであるが、富士通でのPost-Kコンピュータの設計はLEN=4で進められており、この研究の成果が直接的にPost-Kコンピュータに取り入れられるわけではない。