富士通は2016年11月に同社のAIサービスの一環として、「スーパーコンピュータ「京」で培ったプロセッサ開発技術と先端のCMOSテクノロジーを採用した、独自のディープラーニング専用AIプロセッサ『DLU(Deep Learning Unit)』の開発を進め、2018年度からの出荷開始を目指す」という発表を行った。

しかし、DLUがどのようなものであるかは、競合製品と比べて10倍の性能/電力を目指すということしか述べられておらず、謎に包まれていた。

このDLUについて、フランクフルトで開催されたISC2017において、富士通のAI基盤事業本部シニアディレクターの丸山拓巳氏が発表を行い、その概要が明らかにされた。ここでは、丸山氏の発表をもとに富士通のDLUがどうなっているのかを見て行きたい。

アーキテクチャ的にはDLU(Deep Learning Unit)は、ディープラーニングに特化した設計になっている。この点では、GoogleのTPUなどと同じ考え方のプロセサである。

そして、演算精度を最適化することで、競合製品と比較して10倍の性能/電力を目指す。また、京コンピュータで開発したTofuインタコネクトの技術を使って大規模なニューラルネットの処理ができるスケーラブルな設計とするという。

|

|

|

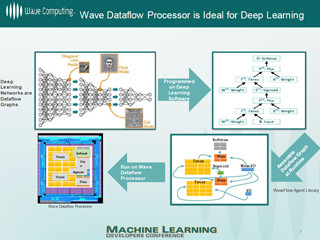

富士通のDeep Learning Unit(DLU)。競合製品の10倍の性能/電力を目指す。また、京コンピュータのTofuインタコネクトの技術を使い、大規模システムまでスケールする設計とする (このレポートのすべての図は、丸山氏のISC2017での発表スライドのコピーである) |

丸山氏は、ディープラーニングの処理を効率よく実行し、高い性能/電力を実現するには、従来のスーパーコンピュータ(スパコン)やGPUのようなアーキテクチャでは不十分で、専用のアーキテクチャのハードウェアを開発することが必要になるという。これは、GoogleのTPU開発チームと意見が一致している。

従来の汎用コンピュータでは、複雑なOut-of-Order実行や倍精度浮動小数点演算などを行って性能を上げているが、ディープラーニング用のプロセサでは、用途に最適化したドメイン特化型のプロセサコアを使い、必要な演算精度を最適化する。そして、超多数の専用コアをチップに搭載し、オンチップのネットワークで結合したアーキテクチャが最適であるという。

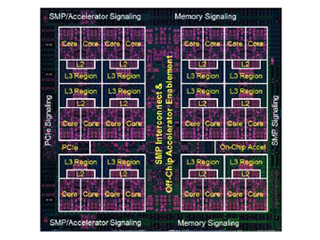

DLUは多数の演算器からなるDPU(Deep learning Processing Unit)を多数集積し、それにホストCPUとのインタフェースと他のDLUと接続するチップ間インタフェース、3次元積層技術を使うHBM2高バンド幅DRAMメモリから構成されている。なお、HBM2はコンパクトで高いメモリバンド幅が得られるので、NVIDIAのPascal/Volta GPUやAMDのRadeon Instinct GPUでも使われている。

DLUは大容量のレジスタファイルを持つ演算ユニットが直接HBM2メモリに繋がっているというメモリ階層とみられる。重みは再利用されないので、キャッシュやローカルメモリは持っても役に立たないという設計である。

後に掲載した図に見られるように、DPE(Deep learning Processing Element)は8並列のSIMD演算器を持ち、DPUは16個のDPEを次の図の青線のリンクでリング状に接続している。また、赤線のリングでDPUをリング状に接続しており、DPEは全体として、2次元のトーラス接続になっているのではないかと思われる。

DLUは、チップ間接続インタフェースを持ち、3次元トーラスの大規模DLUネットワークを構成することができるというスケーラブルな設計になっている。GoogleのクラウドTPU(第2世代のTPU)やNVIDIAのV100 GPUなどは、大規模ネットワークを構成する機能は持っておらず、この点は、富士通のDLUが先行するディープラーニング用のチップに対して優れている点であると言える。

|

|

|

DPUは、DPE(Deep learning Processing Element)をリング状に接続したDPUDeep learning Processing Unit)を多数集積し、超並列に計算を行う。そして、メモリは高バンド幅のHBM2を使っている |

前の図には明示的に描かれていないが、Masterと呼ばれる大型のプロセサコアがあり、それが小形のディープラーニング用コアであるDPUを制御するという構造になっている。マスタコアは、メモリのアクセスとDPUに命令とデータを供給し、実際の演算は多数のDPUが並列に実行する。

この図でもMasterとDPU群を含むプレーンが4枚重なっているように描かれており、DLUは大きく4つに分けられて実装されていると思われる。