なぜGFは7nmに賭けるのか?

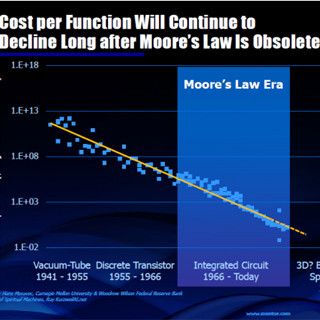

Patton氏は「なぜ、7nmプロセスに賭けるのか」との問いに「それは非常に魅力的だからだ」と答え、その理由を「微細化のスピードは鈍化している。現状の16/14nm、10nmといったプロセスノード名はマーケティングのためのツールにすぎず、微細化により新たな価値を生みだしているとは言い難い状況だ。2年ごとにコストを35%ずつ下げ、性能を20%ずつ上げることのできた時代は20nmで終わってしまった。各社はFinFETを導入することで、やっと14nmを実現しているが、コスト低減はできていない。GFとライバル関係にあるTSMCやSamsung Electronicsは10nmプロセスの実現を目指して競い合っているが、中途半端なプロセスだ。14/16nmプロセスを基準にすると7nmプロセスこそが次の技術ノードとしてコストや性能改善の希望が持てる」と説明する。

2020年から製造導入を目指すEUVリソグラフィ

同氏はさらに「オランダASMLによるEUVリソグラフィの開発が遅れてしまっており、仮に7nmプロセスを用いた製造に使えなくなって、液浸ArFで多重露光を使わねばならなくなったとしても、微細化効果で7nmウェハ製造コストは下げられる」とするほか、「EUVリソグラフィは2020年から製造に使われるだろう。少量なら2018~19年に使用が始まるのではなかろうか」とEUVの導入についての予測を述べた。

なお、GFは、ニューヨーク州立大学Polytechnic Institute(SUNY Poly)と共同で、ニューヨーク州の首都AlbanyにあるCollege of Nanoscale Science & Engineering(CNSE)キャンパスにAdvanced Patterning and Productivity Center(APPC:5億ドル投資し5年契約)を設立し、同キャンパスに自社の研究施設を設置しているIBM、東京エレクトロンなどと協力し、ASML製の量産用EUV露光装置の早期実用化を目指している。

FD-SOIでも差別化はかる

そうした一方でGFは、22nm完全空乏型シリコン・オン・インシュレ―タ(FD-SOI)プロセスにも力を入れている。「22FDX」と名付けられた22nm FD-SOIプラットフォームを有し(図3)、リスク生産を2016年内に始めて、2017年には量産体制を敷く計画だ。同社の顧客は、FD-SOIの利点として、低消費電力、高性能、低リーク電流、それに、トランジスタ性能を顧客が変えられる基板バイアス効果をあげているという。

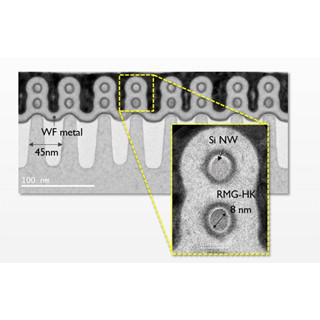

Patton氏は、「高い電流駆動力を備えたFinFETプロセスは、特に先端大規模チップに適している。一方で、IoT向けなど低消費電力が重視される小規模チップにはFD-SOIが選択肢になる。22FDXは、プレーナ型CMOSプロセスと同等のコストで、FinFETと同等の性能を実現できるので、FD-SOIの方が安くつく場合が多い」と述べ、今後も両者を共存させてファウンドリのビジネス展開するため、FD-SOIのさらなる微細化を検討している」と述べた。 さらに同氏は、主流のFinFETとFD-SOIに加えて、新材料・構造を用いた縦型FETや横型FETなどの新奇デバイス研究にも取り組んでいることを明らかにした(図4)。

IBMの半導体事業譲渡を受けた直後のGFは、余剰資産・人材に苦しみ、同時に、親会社のアラブ首長国連邦アブダビ政府系資本も原油価格暴落に苦しんだため、一時は外国資本への身売り話も出ていたが、最近は、中国本土への半導体工場進出を電光石火で決めたりIBMとの協業で技術力を強化して、名実ともにグローバルな規模のファウンドリになろうとしている。