今後のMCUの方向性

さて、ここからはちょっと与太話になってゆくので、そのつもりでお読みいただきたい。Cortex-M7のエリアサイズは(もちろんプロセスによるのだが)どの程度か、という数字は今もってARMからも発表されていない。何しろサンプルにしろ製造しているのはSTMicroelectronicsのSTM32F7のみで、そのSTM32F7も遅れている(こちらの記事では今年第1四半期中にNucleoを出す予定という話だったが、どうも遅れている様で、早くて5月位になりそうらしい)状態ではまだ具体的な指針も出しようがないのだろう。流石にこの規模の製品で、しかも90nm前後だと、ARMがPOPを出したりすることもないから、ある程度製品が揃うまで(NDAベースの資料はともかく公式には)出てこないと思われる。

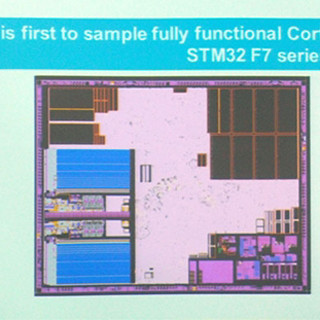

今のところ唯一ヒントになりそうなのは、STM32F7の発表会の際に示されたFloor Planの写真(Photo19)である。この中のCPUコア以外の部分を色分けしたのがこちら(Photo20)で、ラフに言って1MB Flashの2倍ほどの面積を占めているのが判る。

|

|

|

|

Photo19:これはこちらの写真のフロアプランを切り抜いて、少し見やすく色を調整したもの |

Photo20:そもそもこのSTM32F7のダイサイズが公開されていないので正確な数字はだせないのだが |

さて比較対象だが、適当なものがなかったので、英語版のWikipediaのARM Cortex-Mの項目にリンクされている「STM32F100C4T6B」の写真を使わせていただくことにした(Photo21)。

Wikipediaの説明では16KB Flashの構成とあるが、このSTM32F1ファミリーは130nmのembedded Flashプロセスを利用し、最大128KBのFlash Memoryと8KBのSRAMという構成で、ダイをいちいち16KBにあわせて作り直しているわけではないので、ダイそのものは最大構成で製造され、ここから必要な容量だけが有効になっていると思われる。それを加味してエリアの推定を行ったのがPhoto22である。ラフに言えば、Cortex-M3のダイサイズは、128KB Flashの半分、つまりFlash 64KB程度ということになる。Cortex-M7の推定エリアサイズは1MB Flashの2倍近いから、2MB分。なので、両者のエリアサイズを比較する、Cortex-M7のエリアサイズはCortex-M3の32倍という恐ろしい推定になる。

|

|

|

Photo22:下半分の大半はアナログと配線部と思われる。どちらかというとPad limitの方が効いているようで、割とゆとりのあるレイアウトになっている。ちなみにSRAMはFlashの右側の領域と思われる |

もっともこの推定は、embedded Flashの寸法がノードごとに同じ寸法で縮小された場合の計算である。実際には同社のembedded Flashは130nmで0.16μm2が90nmでは0.076μm2とプロセスノード比をやや上回る比率で縮小されており(Photo23)、これを勘案するとほぼ30倍というところだろうか。随分差があるように思われるだろうが、STM32F7の構成が先のPhoto11に近い事を考えると、そう不思議ではない。

Photo12にある8-Layerのmulti-AHB bus matrixもCPUコア部の中に入っていると考えられるためだ。この分を抜くと、いいとこ20倍程度だろう。しかもCortex-M7コアには4KBのCacheとFPUユニットも搭載されている(これもCPUコア部の中に含まれている)から、これを抜いて純粋にCortex-M3とCortex-M7の整数演算部だけを比較するとまぁ10倍というあたりではないかと思う。

さて、大雑把に推定が出来たところで、ちょっと実データを見て見たい。下の表はCortex-M3/M4の実装データをまとめたものである。

| 180ULL | 130LP | 90LP | 40LP | 28HPM | |

|---|---|---|---|---|---|

| Cortex-M3 数字はエリアサイズ(平方mm) |

0.33(*) | 0.18(*) | 0.09 | 0.02 | 0.01 |

| Cortex-M4 | 0.56 | 0.34(*) | 0.17 | 0.04 | 0.02(*) |

| (*)は筆者推定 | |||||

何故かCortex-M3は28HPMがある一方で130/180nmの数字がなく、Cortex-M4は逆に180nmから始まってるあたりが不思議というか面白いのだが、

- 概ねプロセスノードに従った比率でサイズが変化する

- Cortex-M4のエリアサイズはCortex-M3の概ね2倍

という数字になっていることが判ると思う。ここから考えて、Cortex-M7のエリアサイズはCortex-M4の5倍程度で、90LPで0.9平方mm、40LPで0.2平方mm、28HPMで0.1平方mmというあたりに落ち着くのではないかと思われる。本命が40LP以降ならこれは十分許容できるエリアサイズであろう。

さて、ちょっと話が飛ぶのだが、昨今の半導体プロセスを見ると、現時点では40nmが一番低価格(300mmウェハ1枚あたり3000ドル程度)だが、今年中に28nmプロセスが最低価格になりそうという勢いである。これはTSMC/Globalfoundries/Samsungあたりが設備の減価償却を終え、その分価格が下がったことと、Yieldが上がったこと、それと低価格なプロセスが開発されたことなどによる。どうやって低価格化したかというと、HKMG(High-K/Metal Gate)を省いたプロセスを用意したことだ。Mobile向けなどの1~2GHz以上で動くデバイス向けには、それなりに高速動作するトランジスタが必要で、すると絶縁膜を厚くできないから、リークを抑えるためにHKMGが必要になる。ところがMCUなどのデバイスは1GHzを超えることはないから、トランジスタは遅くてもよく、であれば単に絶縁膜を厚くすれば高価なHKMGを利用する必要はない。実際UMCやSMICはこうした低価格オプションをすでにラインアップしており、TSMCも28ULPに同様のオプションを用意しようとしている。

ということで、仮に300mmウェハ(面積は70,650平方mm)を3000ドルで製造できるとすると、100平方mmあたりの製造コストは概ね4.2ドルほどになる。実際はウェハの端っこは使えなかったりするから、多少無駄が出ることを考えて、100平方mmあたり5ドルと試算することにしたい。さて、では今10mm×10mmで100平方mmのダイを製造するとする。このダイのコストはいくらか? というと、実は5ドルではなく、約5.1ドルになる。何でかといえば、図1の様には配置できないからだ。いや配置はできるのだが、製品が作れない。ここには、ダイシング(ウェハからダイを切り出す作業)の際の切り代が含まれていないからだ。このダイシングの最大手は国内のディスコだが、条件にもよるのだが概ね切り代として100μmほどの寸法が必要である。なので、実際には図2の様に10.1mm×10.1mmになる訳で、その分0.1ドルほど価格が上がることになる。

もちろん100平方mmものダイサイズならスマートフォン向けのアプリケーションプロセッサなどのアプリケーションの範疇なので、ここで0.1ドルあがるのはそれほど問題ではない。ところがMCUの場合、ダイサイズが数十平方mm台はおろか、数平方mm台で済んでしまう場合すらあることだ。とりあえずPad Limit(外に配線を引き出すために必要なPad部を取るために最低限必要な面積)は無視して、ダイサイズと製造コスト、およびエリア利用率(ウェハの何%を実際にダイとして利用したか)をまとめたのがグラフ1である。実はコストそのものは、ダイサイズが0.1平方mmでも1平方mmでもさして違わない(0.01ドル/0.06ドル)事が判る。コストが0.1ドルになるのは2平方mm、0.2ドルになるのは4平方mmからである。つまり、むやみやたらに小さくしても原価が下がるとは限らないことだ。

ということで、再びCortex-M7のエリアサイズの話に戻る。先ほどのPhoto20を例に取ると、アナログ回路部はプロセスを微細化しても小さくならない事が多い。これらは何しろ受動部品であり、例えばコンデンサは体積で容量が違うから、プロセス微細化にあわせて底面積を小さくするためには高さをその分増す必要がある。ただこれは現実には結構難しく、結局底面積は殆ど代わらない。これはインダクタンス(コイル)や抵抗でも同じことで、なのでプロセス微細化の恩恵は受けない。ところがそれ以外の部分、つまりCPUコアやSRAM、Flash Memoryなどは全部微細化に応じて寸法が小さくなる。

先ほどのCortex-M3/4/7の寸法の比率が正しいとすれば、Photo20におけるCPUパイプライン部の面積は90nmで凡そ0.9平方mm。FPUやらキャッシュやらmulti-AHB bus matrixやらを全部含んだ面積は2.7平方mm、ダイサイズ全体としては6平方mmあたりではないかと想像される。うちアナログ部は1割の0.6平方mmといったところか。

さて、ではこれを仮に40nmに微細化するとどうなるか? というと、アナログの0.6平方mmはそのままだが、残る5.4平方mmは1.1平方mm程度にまで縮小されてしまう。アナログをあわせても2平方mmに達しないという予測が立つわけだ。ましてやこれを28nmにもってたらどうなるか…というと、アナログとあわせても1.1平方mm程度に収まってしまう計算になる。そろそろ、効率が悪いというか、「もう少し機能を追加してダイサイズ増やしてもいいんじゃないか?」という領域に入ってきているのがお分かりいただけよう。

ましてや、先ほど無視したPad Limitの話が出てくると話はさらに困難になる。Photo21で、ダイの周囲に結構大きな丸い端子が見えているのが判ると思うが、これが外部に信号線を引っ張り出すためのPadと呼ばれる領域である。MCUでもある程度のピン数が必要な場合は、外周にこのための領域をきちんと確保する必要がある。問題は、これを小さくするとむしろコストが上がることだ。こちらは後工程でリード線を貼り付ける作業を行う場所だから、これが小さいと難易度が上がってしまい、下手をするとダイコストよりもパッケージコストが高くつきかねない。手頃な価格にパッケージコストを抑えるためにはある程度のダイサイズが必要であり、今の試算だとSTM32F7をそのまま40nmに持ち込むとやや割高になりかねない。もう少しTCMを増量するとかFlashの容量を増やすなどの形でダイサイズを大きくしたほうが経済合理性に適うだろう。

実はこの経済合理性の壁が、Cortex-M7が今後主流になってゆくだろうと想像される最大の理由である。先のテーブルで、Cortex-M3の28nm HPMを利用したエリアサイズが僅か0.01平方mmであることを示した(これそのものはARMが示している数字である)。つまり正方形だと100μm×100μm、ダイシングの切り代と同じ幅という事になってしまう。いくら周辺機器やメモリをてんこ盛りにするといっても、CPUパワーが無ければそうしたものは宝の持ち腐れになってしまうわけで、Cortex-M7はそれなりにエリアサイズを食うという意味でも、周辺回路や大容量メモリを使い切る性能があるという意味でも、こうした最先端プロセスに適した製品だという訳だ。トランジスタコストを考えれば、古いプロセスを使い続けるよりも先端プロセスに移行したほうが安くなるのは明白であり、となると130nm~90nmにいつまでも留まるというのは価格競争力の低下に繋がるからこれもありえない。先にSpansionがCortex-M7ベースのFM7を40nmプロセスで製造するという話をこちらでご紹介したが、動機は同じ事と思われる。実際、40nmやその先の28nmに移行するMCUはCortex-M7を利用した先端製品に留まり、既存のCortex-M3/M4のほとんどは90nm世代に留まりそうだ。技術的可能性で言えば65/55nmプロセスというアイディアもあるはずだが、いくつかのMCUベンダーに聞いた限りでは65nmに移行するという計画は現状持ち合わせていないそうだ。

実はここまで書いてこなかったもう1つのアイディアがある。それはマルチプロセッサ(MP)化だ。実はMCUとマルチプロセッサはそれほど相性が悪くない。例えば複数の処理を決められた時間で必ずこなす、という(MCUにはよくありがちな)作業を、タイマー割り込みなど使いながらうまくハンドリングするのは結構大変である。ところが複数の処理を別々のコアに割り当ててしまえば、それぞれの処理のレスポンス時間が正確に見積もりできるので、システム構築が非常に楽になる。実際そうしたコンセプトのマルチコアMCUもあるし、ARMベースでもNXPの「LPC4300」の様なCortex-M4/M0の製品が存在する。これだとコアの数だけエリアサイズを食うから、微細化したプロセスには丁度手頃なソリューションである。にも関わらずこの方法が普及しない最大の理由は、現在のARM v7-Mにはマルチプロセッサのための標準サポートが含まれていないためだ。NXPの製品にしても、現在は同社独自の方法でコア間の同期や通信を行っており、折角のARMのエコシステムの利点を損なっている。解決法は簡単で、ARMがMP拡張を施せば済むのだが、冒頭に触れたとおりARM TechCon 2014の折にIan Ferguson氏にこれを確認したところ「Lock Stepはともかく、MPはCortex-Rシリーズの領分で、Cortex-Mでは今のところサポートの予定は無い」と明確に断言されてしまった。そんなわけで、当面はCortex-M7が40nm以降のMCU市場を牽引してゆくことになると思われる。あるいは今年中にはひょっとしてARM v8-Mが発表され、そこにMP対応が入ったりするのかもしれないが、そのあたりまではまだ正確に見通すのは難しい。

|

|

|

Photo24:ARM VP, Segment MarketingのIan Ferguson氏。本来はモバイル寄りの話でのMeetingだったのだが、「Segment MktgってことはCortex-Mもカバーされてるんですよね」と確認の上で無理やりCortex-Mの話に引き込んでしまった。申し訳なし |

この節の冒頭に述べた通り、この段落は基本的に与太話である。どの辺が与太話かといえば、エリアサイズの推定のあたりが非常にラフすぎる&大胆に推定しまくりの計算だからであるが、桁のレベルでは間違ってないとは思っているので、その程度の精度だと理解していただければ幸いである。