従来よりも電流×動作時間が一桁小さいMRAM素子の開発に成功

これに対して、東芝分散研が不揮発性のSTT-MRAM(Spin Torque Transfer-Magnetic RAM)に使う磁性材料の開発から、メモリセルや周辺回路の開発、評価ボードの開発を行い、集中研では、メモリ階層のどこに不揮発性メモリを使い、どのように使えばよいかを研究開発するという分担で、連携を行いながら開発している。

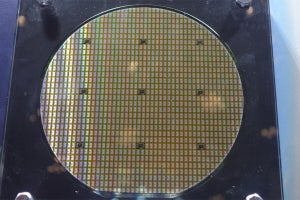

この開発により、図5の青○に示すように、従来学会発表されているものと比べて、電流×動作時間が一桁小さいMRAM素子が作れるようになったという。

図6のノーマリオン型メモリセルの左側の図は、普通の6TのSRAMで、右側の図は、これに磁気トンネル接合素子(MTJ)を追加した基本的なメモリセル回路であるが、これらの回路は赤線で書いたリークパスがあり、電源が入っているとエネルギーを消費してしまう。図6の下側のノーマリオフ型のメモリセル回路は、ワード線の電位を下げて非選択とすると、セルの内部には電源接続がなく、リーク電流が流れないという回路になっている。このため、特別なパワーゲートトランジスタを使わなくても、リークオフができるという。

しかし、STT-MRAMセルの特性バラつきを抑えることは、なかなか大変なようで、図7に示すように、通常モードではAとAPの2素子からの信号を差動で読み出しているが、これでうまく行かないときは、Salvageモードで、それぞれの出力をVrefと比較して、素子ごとに読み出しを行っている。これにより、エラーレートを1/10以下に低減したと報告されているが、通常のECCで救えないくらいのエラーが起こるのでは、実用にはまだハードルがありそうである。

なお、このSTT-MRAMの開発は、東芝とSK Hynixが進めているSTT-MRAM開発とはまったく独立で、量産ラインでの製造ではないとのことで、量産工場で作れば、バラつきを減らせる可能性はあると思われる。

図8は1GHzクロックのARMv7コアでSPEC2006ベンチマークを実行した場合の結果を示したもので、小さくて見づらいが、左下の棒グラフの上側が正規化されたIPC性能、下側が正規化された命令あたりの消費エネルギーを示している。

MRAMとしては右上の表に書かれている1MTJ3Tのものを使う想定で、このセルは50μAの電流で3nsで書き込みができるものである。ARMプロセサのL1キャッシュ、L2キャッシュがともにSRAMという通常の構成のものが3本の組の棒グラフの左側のもので、これを1.0として正規化している。そして、中央のグラフは、L1キャッシュはSRAMでL2キャッシュをこのMRAMとした構成、右のグラフはL1キャッシュ、L2キャッシュともにMRAMとしたものである。

SPEC2006の大部分のプログラムではMRAMをキャッシュに使うことによるIPC性能の低下は10~20%程度であるが、消費エネルギーは30%程度に低減できるという結果になっている。

図9は8コアのハイエンドプロセサでの評価結果であるが、新方式のSTT-MRAMを使うと性能はSRAMと同じで、消費エネルギーは約60%削減できるという結果となっている。

しかし、メモリの周辺回路やキャッシュのロジック部などSTT-MRAM以外の部分のリーク電力がまだ残っており、この部分の改善について研究開発を行っているという。