ADCのジッタにおけるさらなる効果

ADCはサンプリングされたデータ・システムであり、変換が完全にリニアではないため、目的の入力信号、不要な(ブロッカー)信号、およびサンプリング・クロック間の相互変調積とまったく同じ影響を受けます。

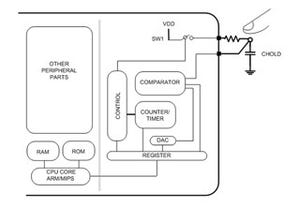

ただし、ADCのためのサンプリング・クロックの仕様を促すもう1つの効果があります。これが、図3に示すアパーチャ・ジッタ効果です。

基本的なコンセプトは、サンプルが取られた時点で存在する不確定性が、三角法によってそのサンプルの振幅の不確定性に変換されるというものです。振幅の不確定性によってADCのSN比低下が起こります。入力信号の周波数が確定すれば、ADCの望ましいSN比に対するRMSジッタのターゲットを決定できます。そのターゲットが達成されれば、ADC内のクロックツリーの内部ジッタが明らかになり、サンプリング・クロックに対するRMSジッタ仕様のターゲットが決定されます。

DACにおけるクロック・ジッタの効果

DACは、伝送パスでベースバンド信号のデジタル信号をアナログ信号に変換し、その後RF周波数に変換して目的の伝送パワーに増幅するために使用されます。無線カード設計者は、DACのサンプリング周波数がカードの受信側の重要な周波数帯域に重ならないように、カードの周波数プランを決定します。このことは、可能な2つのメカニズムによるイメージ周波数発生の影響をDACが受けるため、重要になります。

第1のメカニズムでは、ADCとミキサの場合と同様に、サンプリング・クロック(fLO)と入力信号(fIN)が畳み込まれてN×fLO + M×fINの周波数が発生します。この畳み込みは、コンバータにおける非線形性に起因します。サンプリング・クロック・ジッタの要件に対する影響は、ADCと同様です。

第2のメカニズムは、ほとんどのDACの動作によって必然的に発生する現象です。図4に示すように、サンプリング・クロックの各エッジでは、DACの出力が、デジタル・サンプル値によって表される新しい電圧レベルに非常に高速に切り替わります。この値は次のサンプリング・クロック・エッジまで保持されます。出力は目的の波形にサンプル・クロック当たり1回のみ一致します。

これによって不要なエネルギーが消費されます。加えてほとんどのDACでは、何らかのレベルのクロック・フィードスルーによる影響が生じ、N×fLOでさらなるスパイクが発生します。したがって、サンプリング・クロック周波数をナイキスト基準で求められる値よりも大幅に高くすることで、対象とする周波数をフィードスルーのスパイクが大きく超え、フィルタリングが容易になります。

DACの出力波形はアナログ再構成フィルタを通過することで、不要な周波数が可能な限り除去されます。クロック・ジッタと位相ノイズ特性が適切に制御できれば、フィルタの設計は容易になり、実装コストも低減されます。

サンプリング・クロック上の特定のオフセットにおける特定の位相ノイズ・レベルの要件に加えて、広範な周波数にわたって統合されたRMSジッタの仕様も適用されます。これは、クロック・ジッタによって理想的な出力波形に対する歪みが発生するためです。これはTHD(DACの全高調波歪み)またはSINAD(Signal-to-Noise-plus-Distortion)を低下させるため、無線カードのエラー・ベクトル・マグニチュード(EVM)の低下を防止するために仕様の範囲内に維持しなければなりません。送信側では、クロック・ジッタが低くなると、EVMの改善に直接的に寄与するか、クレストファクタ/ピーク対平均電力比低減回路に対する設計上の制約を緩和する方向に影響します。

無線カード内の位相調整の要件

モバイル・ユーザの多くが、基本的な音声およびデータ伝送サービスに加えて、さまざまな追加的なサービスを希望しています。1つの例としては、携帯基地局からの三角測量によってユーザの正確な位置を特定するサービスが挙げられます。無線三角測量による正確な位置特定は、すべてのアンテナが相互に近接した位相調整の状態で信号を送受信することで、最適に実現されます。そのようなサービスでは、それぞれの位相の相違を50ns未満にして運用するために、別の基地局が必要になる場合があります。無線カードには、同じシステム内の他の無線カードと比較して、どの程度の位相の相違が生ずるかが重要になります。これが、それぞれの無線カードがすべての周波数を内部の単一のクロック入力信号から発生させるもう1つの理由であり、カード上のすべてのクロックについて、少なくとも位相調整を行なう必要があります。

まとめ

RFカードでは、概してノイズの多い単一の入力クロックから、多様なクロックを発生させる必要があります。場合によっては、これらの出力クロックは、入力クロックに対して整数倍にない可能性があります。すべてのクロックは、重要な回路に対するノイズのカップリングを防止するために、全体的なノイズを認識する必要があります。ADCやDACなど、ミキシング専用のクロックは、RMSジッタおよび「ノイズ・スカート」に対する仕様が厳格であり、それによってRF信号パスにおけるブロッカー信号の発生が防止されます。これらのクロックの周波数はカードの特定の導入詳細に応じて慎重に計画されるため、通常は各設計に固有の周波数になります。また、それらのクロックの多くに対して、さまざまな位相遅延調整ができなければなりません。そのため、基本的にカードごとに仕様が異なる、非常に高性能なクロックツリーが必要になります。これは単一のコンポーネントに実装することが理想です。

なお、IDTのNetcomタイミング製品などのデバイスは、RFカードの個々の設計要件に合わせて調整された、このような非常に高性能なデバイスを実現するものです。

著者紹介

Ian Dobson(イアン・ドブソン)

米Integrated Device Technology(IDT)

システム・アーキテクチャ部門ディレクター

IDT入社後、約8年に渡りシステム・アーキテクチャ部門において、カスタマニーズに対応する既存および新たな製品の最適な活用方法の実現に従事。同社入社以前は、主に通信業界においてASIC、回路基板やシステムレベルにおける製品開発に従事してきた。