FPGAはコスト要件や消費電力要件が厳しいアプリケーション、あるいは大量生産を目的とするアプリケーションでますます使用されるようになっています。これらのアプリケーションに付随する様々な課題に対処するため、設計者が必要とするのは、使いやすさ、コスト要件を満たすためにデザインの様々な実装方法を推敲できるフレキシブルな設計環境、そして目標とするコスト・消費電力・性能です。特にデザインが大規模化する場合には、これらがより強く求められます。事実、設計者は、このような目的で進化した設計ソフトウェアを必要としています。この次世代型設計ソフトウェアの一例が、設計ソフトウェア環境「Lattice Diamond」です。

Lattice Diamondは、前世代の設計ソフトウェアに見られる実装エンジン、I/O配置テクノロジ、IP再利用テクノロジ、電力計算とSSO解析、そしてハードウェア/ソフトウェア・システム設計などを基礎として進化させたものです。これに加えてDiamondソフトウェアは、前世代のLattice Semiconductorの設計ツールの持つ3つの主要な機能を拡張しました。これらはデザインの推敲、使いやすさ、及びデザインフローです。これらは全て、コスト要件及び消費電力要件の厳しい設計の課題に対処するために必要です。

デザインの推敲

デザインの推敲機能の主な機能とはすなわちプロジェクト機能の拡張であり、これには"インプリメンテーション(Implementation)"と"ストラテジ(Strategy)"の追加が含まれます。

- インプリメンテーションは、単一プロジェクト内に複数バージョンの定義を可能とし、設計を改善できます。インプリメンテーションは、主として設計構造の定義に使用します

- ストラテジは、インプリメンテーションの"レシピ" に相当し、これを、プロジェクト内の任意のインプリメンテーションに適用することも、プロジェクト間で共有することもできます。ストラテジは、ソフトウェアツールに対して、設計の実行または実装方法を指示します

- 設計プロジェクトは、任意のインプリメンテーション内に、Verilog、VHDL、EDIF、及びスケマティック(回路図)ソースの混在が可能です

- 設計制約、タイミング解析、電力計算、及びハードウェア・デバッグツール用など、複数のファイルに対応します。ファイルは、必要に応じて選択及び有効化/無効化が可能で、それにより、個々のツールが開いたときの振る舞いや、デザインの実装方法を決めることができます

- ランマネージャ・ビューは、最良の結果を実現するために、デザインを推敲する目的で、複数インプリメンテーションの並列処理を可能にします

ランマネージャを利用すると、設計者は、1つのプロジェクトで複数のインプリメンテーションを選択し、それらの結果を比較できます。

インプリメンテーションについて

インプリメンテーションは、プロジェクトのために、設計構造のエレメントを定義します。その中にはソースコード、設計制約ファイル、及びデバッガ挿入などが含まれます。インプリメンテーションは、設計を行うために必要な原材料とも言えます。単一プロジェクトで複数のインプリメンテーションを使用する典型例として、最良の結果を出すために、様々なアーキテクチャを試す場合が考えられます。

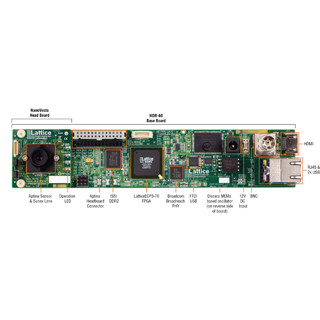

シンプルな例として、1つのインプリメンテーションでメモリの推論を使用し、他方のインプリメンテーションでインスタンス化メモリを使用することなどが考えられます。設計者は、既存のインプリメンテーションをコピーすることで新しいインプリメンテーションを生成し、これにより実質的に既存のソースをそのまま新インプリメンテーションでも使用できます。Diamondファイルのリストビュー(図1)は、アクティブになっているインプリメンテーションの"mixedcounter"が表示されています。