そして、HPC-ACEの第3の拡張はソフトウェアの指定でキャッシュを分割して使えるという機能である。

キャッシュは、頻繁に使用するデータを高速、小容量のメモリにバッファすることによりメモリアクセスを高速化する機構であるが、ハードウェアにはそれぞれのデータが将来、どう使われるかは分からない。例えば、大きな配列の全要素の和を計算するような場合には、次々と配列要素をキャッシュに読み込むが、これらの要素は一度使えば終わりで再利用されない。このようなデータを格納するために、頻繁に使うデータがキャッシュから追い出されて性能が下がるという問題がある。これに対する1つの解はCELLプロセサで採用されたローカルメモリであるが、これはソフトウェアが意識してデータの入れ替えを行う必要があり、プログラミングが難しいという問題がある。

これに対する富士通の解が、このソフトウェア制御の分割キャッシュである。キャッシュをセクタ0とセクタ1という2つの領域に分割する。そして、メモリからデータを読み込む場合にどちらのセクタに読み込むかを指定できるという命令拡張を行っている。例えば、頻繁に再利用することが分かっているデータはセクタ1に読み込み、その他一般のデータはセクタ0を使うというようにすると、一過性のデータで頻繁に使用するデータが追い出されることが無くなる。ソフトウェアではどちらのセクタに読み込むかの指定が必要となるが、これを間違えてしまっても性能が下がるだけで正しい実行結果が得られるので、プログラマに対する負担も少ないうまい方法である。

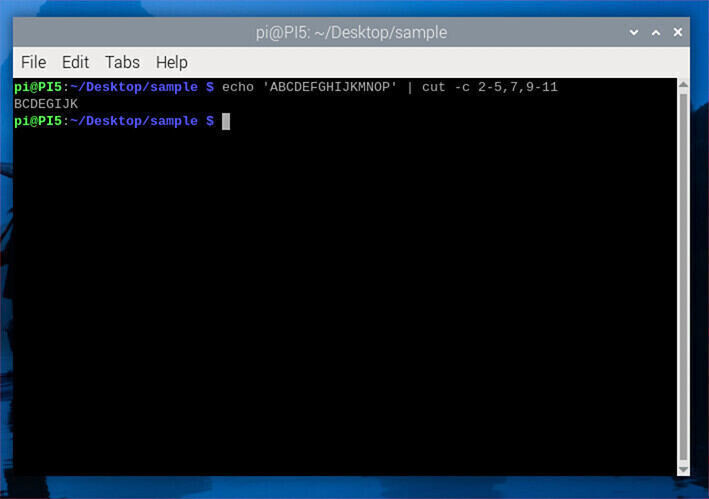

このようなHPC-ACEのアーキテクチャ拡張の効果を示すのが図4である。

このグラフは2.5GHzクロック、4コアのSPARC64 VIIと、2.0GHzクロック、8コアのSPARC64 VIIIfxの実行時間を比較したもので、左側の分子動力学アプリケーションの場合は2.4倍の性能、右側の流体力学計算の場合は2.6倍の性能となっている。コア数×クロックでは1.6倍であり、これを超える分が、ほぼHPC-ACEによる性能向上と考えることができる。少し見難いが、棒グラフの上から2番目の白っぽく表示された区分の演算結果待ちの時間がSPARC64 VIIIfxでは大幅に減少している。これはレジスタ拡張の結果、ソフトウェアパイプラインがうまく動くようになったものと考えられる。

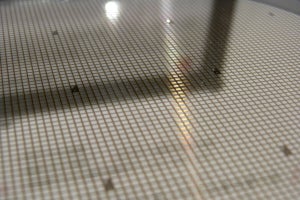

SPARC64 VIIIfxチップは富士通の45nmプロセスで製造され、8コアと5MBのキャッシュを搭載した22.7mm×22.6mmのチップで、トランジスタ数は7億6,000万である。チップ面積としては513平方mmであり、POWER7の567平方mmと比べると一回り小ぶりではあるが、かなり大きなチップである。

そして図6に示すコアのレイアウトでは左側中央のFPR+FUBと書かれた浮動小数点レジタの面積がかなり大きくなっていることが見て取れる。

8コアで各コアが8演算/サイクルという点ではSPARC64 VIIIfxとPOWER7は同じであるが、クロック周波数では2GHzと4GHzと2倍の違いがあり、チップ当たりの演算性能ではPOWER7の方が2倍高い。しかし、これは富士通はクロック周波数を落として消費電力を下げるという設計思想を採った結果で、8コアプロセサで58Wという低い消費電力を達成している。

POWER7の消費電力は200Wと言われており、これが正しいとするとGFlops/Wでは、SPARC64 VIIIfxは2.2であるのに対してPOWER7は1.28であり、富士通の方が1.7倍あまり高いエネルギー効率となっている。

この消費電力の低減にはパイプラインの各ステージやSRAMマクロなどの細かい単位で、使用していないサイクルにはクロックを止めるというクロックゲートを徹底している。また、リーク電力を下げるために、3種のスレッショルド電圧(Vth)のトランジスタを使用しており、リーク電流の大きい高速トランジスタは全体の0.1%しか使用していないという。そして91.5%がリークの少ないノーマルトランジスタで、時間調整のために大きな遅延が必要な8.4%の部分ではさらに低リークの高Vtトランジスタを使っている。

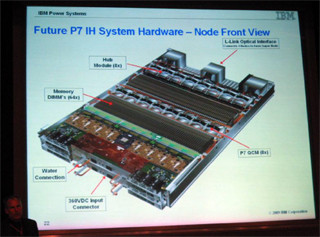

また、図7に示すように、CPUモジュールとインタコネクト用LSIを水冷し、チップ温度を30℃という低温に保っている。

トランジスタのオフリーク電流は温度に敏感で、この冷却によりリークによる消費電力を12Wから5Wに低減しているという。また、チップ温度は故障率にも大きく影響し、チップ温度を30℃に下げると85℃の場合に比べて1/100程度の故障率になるという。次世代の10PFlopsスパコンでは10万個近いSPARC64 VIIIfxプロセサが使われることになるので、消費電力と故障率の低減は極めて重要である。