これからのトランジスタ性能向上技術

また、トランジスタを見てみると、フィンピッチを1/3に短縮し、性能を3倍に引き上げられる可能性は十分にある。

そして、フィンの替わりにシリコンナノワイヤを使えばチャネルの密度を2倍に高めることは可能で、トータルの性能向上は6倍となる。

さらにNMOSとPMOSのナノワイヤをスタックすれば、チャネル密度は2倍になり、総合では12倍の性能向上になる。

それにダイを重ねて実装する技術を使えば、トランジスタ密度はさらに2倍となり、全体の性能向上は約50倍となる。

消費電力の低減も可能に

トランジスタ密度は、こんな風にして増やせるかも知れないが、消費電力が問題という指摘もある。しかしそちらも電圧スケーリング、キャパシタンススケーリング、新パッケージング、新アーキテクチャなどで、1/50への削減は見込める。

-

信号振幅を減らす電圧スケーリング、寄生容量のスケーリング、パッケージングの改善、クロック周波数のスケーリング、それに加えて新アーキテクチャによって電力を1/3程度に減らす見込みを合わせて、1/50への電力低減を見込む

パッケージも微細化し、2D、2.5Dの実装、3Dの実装を行っていけば、電力を1/10に減らすあたりまでは道は見えている。さらにバンプピッチを10μm以下に微細化できる技術を開発すれば、この部分の低電力化も夢ではない。

バンプピッチの低減であるが、現在のIntelの最高峰のFoverosテクノロジでもバンプピッチは50μmであるが、次世代のHybrid Bondingで10μmピッチを実現すればキャパシタンスが減り、低電力化が可能になる。

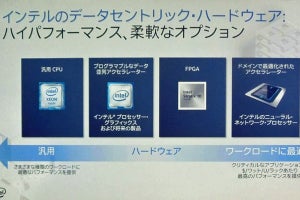

Intelは実装技術の開発にも熱心で、Kaby Lake G CPUでは複数チップをインタポーザに載せる2Dテクノロジを使っている。また、Agilex FPGAでは、IntelのFPGAとファウンドリで作ったI/Oチップ、メモリメーカーの作ったHBMといった製造プロセスの異なるチップを1つのインタポーザ上に搭載した。

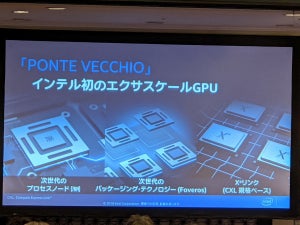

そして、Lakefield CPUでは複数ノードの半導体テクノロジで作ったチップを組み合わせて1つの製品とする実装を行った。右下の写真は、エクサスパコンのAuroraに使われる予定のIntel製のPonte Vecchio GPUの写真で、GPUチップの製造はTSMCで、GPU全体としては複数のファブの異なるテクノロジのチップが混在する製品となると言われている。また、巨大なGPUチップを作るのではなく、複数のチップレットを組み合わせて色々な製品が作れる設計になっていると言われている。