CPU

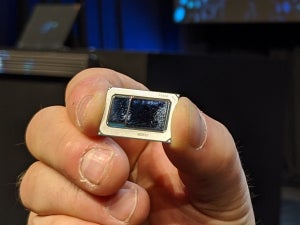

さてこの10nm SuperFinを採用する最初の製品がWillow CoveベースのTiger Lakeである(Photo11)。Willow CoveではMLC(Mid Level Cache:要するにL2キャッシュ)が1.25MBに拡大されたほか、分岐制御の高速化が図られたとしている。またSuperFinの採用で、従来よりも動作周波数の引き上げが可能であり、また同じ動作周波数なら低い電圧で動作する、としている(Photo12)。実際WebXPRT3を実施した場合、Willow CoveはSunny Coveよりも高い動作周波数で動くことがデモで示された(Photo13)。

これに組み合わせるFabric/Memoryであるが、Fabricの帯域を倍増化したほか、LLC(L3キャッシュ)を12MBに引き上げている。またIce LakeのDDR4-3200/LPDDR4X-4267に加え、LP5-5400もサポートすることが明らかにされた。さらにGNA 2.0を新しく追加している(Photo15)。またDisplay Engineにも改良が施されたほか、ISPはIPU6という名前になり、最大6つのImage Sensorに対応できる様になったとする(Photo16)。

-

Photo15: Neural AcceleratorはSunny Coveにもあったが、Gaussianに関してはTremontで実装されていたもののSunny Coveには実装されていなかった。これをCPUコアの外に搭載した形だ。

GPUに関しては16EUのクラスタ×6でトータル96EU、更に専用の3.8MB L3キャッシュが実装されるとする(Photo17)。

Photo18がTiger Lakeの全体の構成だが、他にPCI Express Gen4の対応とかUSB 4.0の実装なども行われた。

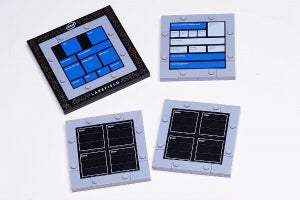

さて、CPUではもう一つ、Alder Lakeの存在も明らかにされた(Photo19)。ただ現状は"Alder Lakeはパフォーマンスとバッテリーライフの両方を狙ったものだ"という以上の説明はなかった。とりあえずLake Fieldの後継であるHybrid構造になることだけは明らかであるが。