その他もろもろの話

以上でDeep Diveの分析は完了であるが、Next Horizon Gamingの際に説明された中で、ここまで紹介していない話がいくつかあるので、これをまとめて紹介したいと思う。

まずSecurity。もともとRyzen系はSpectre/Meltdownから始まる一連の脆弱性の影響が非常に少ない(皆無ではない)アーキテクチャであり、その後登場した諸々の脆弱性の影響も殆ど無いのだが、一応Spectre及びSpectre V4に関しては若干影響をうけている。これはOS及びファームウェアで対応可能であり、実際既にOS側で対策が完了しているが、Zen 2ではこれにハードウェアでの対応を追加したとしている。先にPhoto03で、一番下に"Hardware-enhanced Secutiry mitigations"とあるのがそれである。

-

Photo25: ただ私見を言えば、Intelのアーキテクチャは古くから内容も公開されており、よく研究された結果として脆弱性を見つけやすかったという側面もあり、今後はZen固有の脆弱性とかが発見されても不思議ではない。現時点で脆弱性が少ないのは、単に登場して間もない(ために研究が進んでいない)から、という可能性は否定できない。

次にまたもやInfinity Fabricについて。先に、CCXを跨いでのデータ転送は、どうも一度cIODのInfinity Fabricを経由するようだ、という推察を書いた。ただこの場合、例えばSenseMIとかXFRの様に、殆どリアルタイムで処理が必要とされ、かつInfinity Fabricを利用する機能が猛烈に遅くなりそうなのが気がしたのだが、その回答がこちら(Photo26)である。

この図を見ると、CCD0/CCD1とcIODの3つのダイの上に、SMUというブロックがあるのが判る。これはSystem Management Unitであるが、どうもこのSMUがInfinity FabricのうちControl Fabticの制御を行っている模様だ。元々Infinity Fabricは、制御を行うControl Fabricとデータ転送を行うData Fabricの2つの要素から構成される。Photo27はZen世代のダイの内部構造だが、ほぼ全てのコンポーネントがピンクのControl FabricとブルーのData Fabricの両方に繋がっているのが判る。

さて、Zen 2ではこれがどうなったか? というと、Data Fabricについては制御そのものはcIOD側に投げており、ところがControl Fabricについては原則自身のSMUで処理し、他のユニットに関係する時だけ、SMU経由からGMI2経由でcIOD側のSMUに連絡する、という形をとっているようだ。恐らくCCD側にData Fabricまで載せてしまうとダイサイズが増える=コストが増える事を嫌っての措置だったと思われる(あと、CCDを跨いでのアクセスが、最悪Fabricを3つ跨ぐ事になるのでLatencyも増えるだろう)。その代償は、同じCCD内の2つのCCX間の通信が遅くなることだが、それはL3をCCXあたり16MBに増強して、通信の頻度を減らすという形で対応したのだと思われる。

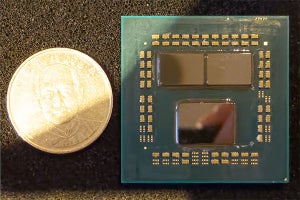

ただこうしたマルチチップ構成とした結果、Package Substrate(ダイを載せている基板)にも新たなチャレンジが生まれた。要するに信号ピンが大量に増えており、しかもCCDは7nmプロセスを利用したことで74平方mmという非常に小さなダイになった。となると当然配線密度というか、そもそもダイとPackage Substrateを繋ぐBallの実装密度が大幅にあがることになる(Photo28)。

-

Photo28: 勿論これは、それこそTSMCのCoWoSの様に高コストで良ければいくらでもやりようがある(HBM2も同じだ)が、単価の高いEPYCはともかく低価格なRYZENでこれを実現するのが難しいという話である。

Ballの密度が上がると、実装時にBall同士がくっついてしまう可能性がある。これを防ぐためにはBallを小さくまとめる必要がある。そのための策が、パッケージからまず銅の柱を生やし、そこにBallを形成するというアイディアだったそうだ(Photo29)。

-

Photo29: 副次的な効果として、この柱の高さを調整することで、CCDとcIODの高さを同一に出来る(これでヒートスプレッダが装着しやすくなる)というメリットがある。ただ、この柱をそもそも構築するのにひと手間必要になる訳で、これはこれで大変である。

Package Substrateで言えば、PCIe Gen4への対応も色々大変であり、これに向けて新しい低損失材料を採用するといったチャレンジもあったそうだ(Photo30)。また、なにしろ

Infinity Fabric:4GHz弱

Memory:4GHz弱

PCI Express:16T/sec

というHigh Speed Signalがはい回っている訳で、Substrate上の配線もかなり困難だったらしい(Photo31)。結果、SubstrateはZen世代から2層増えた12層基板になったそうだ。

-

Photo30: "We took some risks that paid off"というのは、価格面もさることながら、量産過程でその低損失材料を利用する事の知見が十分では無かったために、色々チャレンジだった模様だ。

おまけに、製品ラインナップに2ダイ(CCD+cIOD)と3ダイ(CCD×2+cIOD)の製品が混在するので、生産ラインも色々大変だったそうだ(Photo32)。

-

Photo32: 2ダイと3ダイで完全に生産ラインを分ければ簡単になるが、デマンドに対して生産調整を掛けにくくなる。あくまでも1つの生産ラインで作り分ける方が、製造・販売を行う側としては便利であり、そのせめぎあいの結果、頑張って生産ラインを何とかする方向になった模様。

Zen 2の内部分析を終えて

ということで、AMDによるZen 2 Deep Diveの内容をご紹介すると共に、合わせて内部分析を行ってみた。

筆者の感想を述べれば、確かに色々工夫がなされており、Zen 2コアの性能は確実に向上している。

Chiplet Architecureの採用でメモリアクセス、あるいはCCXを跨いでのコア間通信などはかなりオーバーヘッドが増えているが、Infinity Fabric自身の高速化(というか、低Latency化)や大容量L3キャッシュの搭載などで、Chipletに起因するボトルネックはほぼ解消している、というか普通に使う分にはまずそうしたボトルネックを感じる事が無い。Threadripperではこのあたりのダイ間接続のボトルネックがアプリケーション性能にガッチリ響いており、使う側の工夫が求められたものだが、そうした必要は第3世代Ryzenには不要である。

何というか、実によく出来た製品になった、という事が改めて確認できたと思う。

発売後の状況も悪くないようで、さすがにハイエンドのRyzen 9 3900XやRyzen 7 3800Xはかなり品薄ではあるが、その下のモデルについては入手性も悪くないようだ。恐らくハイエンドについても、それほど時間が掛からずに入手性が改善されるだろう。

先にお届けした性能評価の最後で「よくぞここまで性能を高めた、というのが率直な評価である」と書いたが、内部解析の結果としては「よくぞここまで内部を作りこんだ」と評したい。非常によくできたCPUだと思う。