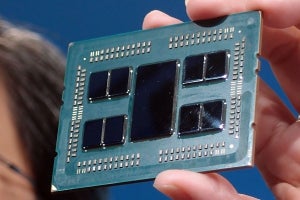

このZen 2のダイを搭載する、RomeベースのEPYCはどんな構成か? Photo09のように、EPYC“Rome”ではすべてのI/OがI/O Dieに集中しているが、それとは別に基調講演の中で今後のEPYCロードマップとしてRomeとMilanが示された。そのうえで、「Romeは現在のNaplesのプラットフォームと互換性がある」「Romeは次のMilanとプラットフォーム互換性を持つ」という2点が説明された。また新たな機能として、PCIe Gen4およびCCIXへの対応が表明されている。

これらを元に、I/Oチップの内部を推定したのが図4である。まずメモリコントローラ。Photo08では8つのメモリコントローラが描かれているが、各々2chのDDR4を接続できると筆者は推定する。

理由は簡単で、そうでないとコア数と帯域がマッチしないからだ。Zen世代の場合、大体4コアとDDR4 1chがちょうどマッチする設計になっている。Ryzenが8コアで2ch、EPYCが最大32コアで8chのメモリバスを持っていることからも明らかだ。であれば、最大64コアのRomeでは最大16chのDDR4を搭載できないと辻褄が合わない。また、一般的に1つのメモリコントローラから2chのメモリバスが出るのは普通で、そう考えるとRomeのI/Oダイは16ch分のDDR4を接続可能になっていると考えるべきだと思う。

ただそうなると、Naplesとの互換性は?という話になるが、そもそもEPYCで使われているLGA 4094パッケージの全部のピンが既に使用済み、とは考えにくい(本当はこれも仕様書を確認したいのだが、あいにくAMDはEPYCやThreadripperのピン配置を公開していない)。

筆者の推定としては、8つのメモリコントローラのうち4つ分の8chに関しては、既存のEPYCと同じピンを利用しており、残る4つについては、現状では未使用のピンにあてているというものだ。なので、Naplesのプラットフォームを利用すると8ch分のみ利用可能、Romeのプラットフォームを利用すると16chがフルに使えるという形だ。言ってみればNaplesがSocket AM2にあたるとすれば、RomeはSocket AM2+に相当する。そして次のMilanはSocket AM3になるわけだ。

タイミング的には、Milanの世代はそろそろメモリI/FとしてDDR5が射程に入ってくる。DDR5になると帯域が倍増するから、仮にコア数がMilanでさらに倍増したとしても(個人的にはさすがにそれはないと思う)、メモリch数はそのままで行ける計算。アップグレードパスとしては非常にリーズナブルなシナリオだと思う。

これに向けて、RomeではDDR5世代の信号に対応したピン配置が行われ、ただし信号はDDR4になる(DDR5世代ではまた信号線が増えるらしいので、当初からその増える信号のレイアウトに対応しておく)。これによりMilanが登場したときに、Rome Platformを使うとDDR4の16ch構成、Milan Platformを使うとDDR5の16ch構成となる、というアップグレードパスになるのではないかと筆者は予測している。

次がPCIeで、PCIe 4.0に対応しているほか、CCIXのサポートもここで含まれる。ただ、これもNaplesのプラットフォームを使う限りはPCIe Gen3相当で動くことになるだろう(そしておそらくCCIXは利用不可)。理由はプラットフォームというか、マザーボード側にある。

ちょっと古い話になるが、PCI Express Gen3でも一部のケースでReTimerが必要という話を以前ご紹介した。ところがPCI Express Gen4では、このReTimerがほぼ必須になる。速度が倍増した関係で、配線を引き回せる距離が半減しており、特にサーバー向けのマザーボードでは配線の間にこのReTimerを挟み込んでおかないと、PCIe Gen4では利用できない。

ところが既存のマザーボードでこれを搭載している製品は皆無に近く、結局、PCIe Gen3相当まで速度を落とさないと利用できないのだ。先のメモリの話もそうだが、こちらの問題もそういうわけで、Naplesプラットフォームをそのまま使うことはできるが、フルに使おうとすると、きちんとPCIe Gen4に対応したRomeプラットフォームに切り替える必要があるということだ。

このPCIe Gen4は、CCIXや(2 Socket構成の場合の)Infinity Fabric Linkとして利用されることになる。なので、PHYそのものは最大で25GHzくらいまでの動作が可能になっていると思われる。この絡みで、CCIX対応のMAC層も用意され、これがPCIe Gen4 PHYと接続されるだろう。図4には記載していないが、M.2の関係でSouthbridge Functionに含まれたSATAコントローラから、PCIe Gen4 PHYにSATAの接続も伸びているはずだ。

“∞PHY”は、要するにCPUダイと接続するためのInfinity FabricのPHYである。こちらはMCM上を通るので、信号レベルの変換などがおそらく必要になる。個人的には(図1にも書いたが)、x8相当くらいのレーン幅になっているのではないかと予測している。

次の「L4 Cache & Snoop Filter」である。L4はともかくとして、Snoop Filterとは何か? 今回8つのCPUダイがあるわけだが、それぞれのダイ上にあるL1~L3キャッシュが書き換わった場合、その領域と同じアドレスをキャッシュしている別のダイは、内容を書き換えないといけない。

要するにCache Coherencyを取りますという話であるが、問題はそのためのSnoopingを何も考えずに行った場合、そのSnoopingの処理だけで馬鹿にならないトラフィックが発生してしまう。そこでI/Oダイの側に、「どのコア(orダイ)がメモリのどのアドレスをキャッシュしているか」を保持しておく。書き換えが発生したら、そのアドレスをキャッシュしているコア(orダイ)に対してだけSnoopingを行えば、Snoopingのトラフィックを最小限に抑えられる。

実はこの仕組み、かつてはHT Assistとして6コアOpteronに搭載されていたものである。EPYC……というかNaplesの場合は、そもそもメモリコントローラが各CPUダイに分散しているから、それぞれでSnoop Filterを持つと効率がよろしくないという問題があった。ところがRomeでは、メモリコントローラが一カ所に集まっているから、Snoop Filterを搭載したほうが効果的である。

余談ながら、Snoop FilterはIntelのSkylake-SPにも搭載されている。コアの数が増えるに伴い、キャッシュも分散されて配置されるようになると、こうした技法を取り入れるのはもはや必須と言える。

ただしこのSnoop Filter、UMAモードで利用する場合には必要だが、NUMAモードだとそうではない。例えば8つのダイそれぞれで別々のOSを動かしており、それぞれ異なるメモリアドレスを割り当てていれば、そもそもSnoopingが発生しないからだ。なので、構造としてはL4キャッシュと兼用する形で、動作モードとしてL4キャッシュの一部がSnoop Filterになるような仕組みと考えるのが自然だ。

もう一つ余談を。先にマイクロアーキテクチャのところで、L3がInclusiveになったのではないか? という可能性を示したが、これはSnoop Filterの動作に関係してくる。もしL3がExclusiveだった場合、Snoop Filterは64個のCPUコアすべてのL2キャッシュ+8つのL3キャッシュについて、それぞれがキャッシュするメモリアドレスを保持して、それに基づきFilteringを行うことになる。これは猛烈に大変だ。

ところが、L3がInclusiveの場合、Snoop Filterはもはや各コアのL2は気にする必要がない。L3がInclusiveならば、L3を見ておけば済むからだ。Snoop Filterが実装されている、という前提ではあるが、これが理由でL3はInclusive化されたと筆者は考えている。

L4キャッシュの容量がどの程度あるかは不明だが、例えばPhoto03で言えば、8MB分のL3キャッシュの容量は大体22平方mm。仮にI/Oダイの面積の半分をL4にあてたとすれば、80MBものL3が確保できることになる。このあたりはそれぞれのCPUダイがどの程度のL3を搭載するかにもよるし、L4についてはRyzenのL3よりもさらに高密度なトランジスタを使う可能性もあるから、現状なんとも言えない。ただ大容量のL4が搭載されるであろう、ということだけは予言できる。

最後がSouthbridge Functionsで、これはSATA/USB/etc……を統合したものだ。サーバー用途だからUARTなどが含まれる一方、Soundなどは統合されないと思われる。また、データマネジメント用にEthernet(おそらくGbE程度だろう)が1ポートか2ポート、搭載されるかもしれない。

ということで、Rome世代のEPYCの構造をまとめたのが図5となる。これは最大構成であり、当然これより下位グレードの48コアとか32コアの製品もあり、その場合はCPUダイが6つあるいは4つという構成になるだろう。32コアの製品に関しては、8ダイながら各ダイあたり有効なコアが4つ、という構成を取る可能性もある(理由は次のRyzenのところで)。

基本的にこのRome世代の製品は、すべてNaplesプラットフォームと互換性を持つから「挿せば動く」とは思う。だが、メモリバス幅とのマッチングミスの問題はあるわけで、現実問題としては32コアあたりの製品がアップグレード向けとして利用され、48コア以上の製品は新しいRomeプラットフォームに移行をおすすめ、というあたりになるのではないかと思う。

ちなみにThreadipperに関しても、同じプラットフォームを使うことになると思われるが、こちらはさらにDDR4のチャネル数が減る(4ch)。技術的には8ダイ64コアは可能とはいえ、現実問題としてCPUダイは2つか4つで、最大でも32コア程度にとどまる気がする(さもないとバランスが異様に悪くなる)。