AMD CPU - "Zen"コアベースの製品はいつごろ登場するのか

AMD CPUにとって2015年は端的に言えば「何もなかった」年である。理由は単純で、20nmプロセスは使い物にならず、かといって16/14nmプロセスを使うには時期尚早で、結局28nmプロセスを引き続き使わざるを得なかったからだ。

こうなると新アーキテクチャの投入もちょっと難しい。結局Kaveri RefreshであるGodavariを5月に投入したほか、6月には一応単なるRefreshではないCarrizoも発表したが、残念ながらこちらはMobile向けのBGAパッケージということもあって日本ではそもそも搭載製品すら殆どお目にかかれないという悲しい状況であった。

ただ、2016年のAMDはいくつかの新製品を投入できる。最初に投入されると思われるのは、Merlin Falocon(Photo17)ベースのAPUである。Merlin Falconは元々はEmbedded向け製品ということで低く消費電力を抑えた形で2015年10月に発表されたが、現状15-35WとされるTDPはそのままMobile向けに利用できるし、TDPを45/65Wまで引き上げれば現在のA8程度の性能は優に出せる。

コアそのものはCarrizoと同じExcavatorなので、高速動作には向いていない(から、A10-7850K/7870Kの様に4GHzオーバーは望めない)が、3.6GHzあたりまでの動作周波数は実現できそうだ。また、MemoryにDDR4-2400を組み合わせることでGPU性能の更なる引き上げが可能で、トータルとしてはバランスの良い製品になると期待できる。

このMerlin FalconベースAPUは、Socket AM4という新プラットフォームの露払いの役割を果たす。従来のAMDの製品はいずれもSocket FM2+(とSocket AM3+)で、DDR-4に対応していなかった。ZenもこのSocket AM4を利用する予定だが出荷時期がやや遅くなるので、まずはMerlin FalconベースでSocket AM4プラットフォームを展開しようという訳だ。

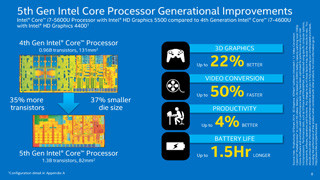

これに続きZenベースのAMD FXプロセッサ、及び後追いの形でZenベースのAPUも展開されることになっている。いまのところ最初に登場する(or させたい)と計画されているのはAMD FX向けのGPUを持たない(恐らく)8コア構成の方で、続いて4コア+GPU(恐らくGCNベースで12~16CU程度)のAPUが追加される形になる予定だ。これに関しては2015年10月のInvestor MeetingでLisa Su CEOが明確に示している(Photo18)。

|

|

Photo18:まずはハイエンドデスクトップで、次がサーバー向けという順序なので、ここにGPUが入るとは思いにくい。また、"First full year of revenue projected for 2017"というあたり、メーカーに出荷は2016年中に行われるが、それが売り上げとして計上されるのは2017年ということは、出荷は年末ぎりぎりの可能性もある |

ただ、実際にどちらが先に出せるかというのは、これまたプロセス側による部分が大きい。APUの方はMerlin Falconの置き換えという位置付けの製品で、CPUコアの側の動作周波数をそれほど引き上げなくても良いが、AMD FXの方はCore i7のマーケットを少しでも侵食しようと思うと、結構頑張って動作周波数を上げる必要がある。こちらはなかなか難しいと想像される。

そもそもZenはIPC比でExcavatorコアの40%アップとされる。逆に考えると動作周波数を40%落としても性能は一緒ともいえる。既存のA10-7870Kは定格3.9GHz/最大4.1GHzとなっているが、Zenベースなら2.3GHz/2.4GHz程度まで動作周波数を落としても辻褄が合う計算だ。実際はもう少し引き上げて2.5~2.6GHz程度で動かしても十分競争力のある商品になるだろう。

ところがAMD FXの方は、それこそSkylakeと競合するわけで、もしハイエンドで争うつもりなら、4GHz近くまで引き上げないと厳しい。はたして、これがSamsung/GLOBALFOUNDRIESの14LPPで可能か? というのが問題である。

Zenのアーキテクチャについて、かなりの部分(特に実行ユニット部)は、AMDが並行して開発しているARMv8-AベースのK12と共通と思われる。そのため、実際にはサーバー向けの64bit ARMとほぼ同等のFO4の設計と考えれば良い。要するにCortex-A57とかCortex-A72をベースにしたサーバー向けプロセッサと大体同じだ。

これらのプロセッサの動作周波数は、BroadcomによるCortex-A72での実装を見ると、軒並み3GHzあたりが上限であるのが分かるかと思う。

これらはいずれもTSMCの16FF/16FF+をベースとしたものだが、これをSamsung/GLOBALFOUNDRIESの14LPPに切り替えたからといって簡単に4GHzになるかというと、さすがに無茶ではないかと思う。恐らく想定される周波数は3GHz台前半というあたりだろうが、それすら結構な時間を掛けて最適化を図らないと難しいと思われる。

そう考えるとAMD FX向けのZenが2016末というのは真っ当というか当然そんな感じだろうなという気がするし、逆にもっと動作周波数が低くても商品として成立する(=最適化をそれほど掛けなくても売り物になる)APU向けが先に量産に入る可能性は当然ありえるだろう。

ちなみにZenのアーキテクチャというかパイプライン構造に関しては、AMDでGCCの開発に携わっているVenkataramanan Kumar氏が2015年10月に、GitでZen用のPatchを投稿しており、ここからある程度の推察が可能となっているので、具体的に紹介すると

- Decoderは4命令/cycle。これは例えばCore 2とかCore iの様にSimple Decode×3+Complex Decodeというものではなく、K7/K8/K10の様に対称型の構成

- 実行ユニットはIEU(Integer Execution Unit)が4つ、FP(FPU)が4つ、AGU(Address Generation Unit:Load/Store Unitの事)が2つの合計10個。

- IEUに関しては4つの実行ユニットはほとんどの命令で対称型(どの実行ユニットでも同じようにInteger実行が可能)。

- 2つのAGUもやはり対称型。

- FPUのみ非対称になっており、命令を実行できる組み合わせに制限がある。基本FPUの幅は256bitであり、256bitのFMA演算(乗算+加算)を同時に2命令実行できそうに見えるが、patchによれば例えばavx256_fma命令はFPU0+FPU3、もしくはFPU1+FPU3の組み合わせでしか実行できない(FPU2が使われない)。このため、FPUの最大の演算幅は256bitとなる。

といったことが読み取れる。ちなみにこのPatchの情報は、ドイツのMatthias Waldhauer氏に教えていただいたものだ。

図1はこの情報を基に筆者が推定したZenコアの内部構造である。ZenコアがK12コアと実行ユニット部の構造を共有している可能性が高いことを考えると、実行ユニットで利用されるμOpはかなり抽象度が高いというか、従来のx86のことだけを考えたものとは異なる可能性もある。

すると、x86からダイレクトにμOpを生成するのではなく、一度中間命令に変換して、そこから最終的なμOpを生成するように思える。AMDはK8/K10の世代でこれにあたる構造をすでに実装しており、IntelのMicroOps Fusion/Macro Ops Fusionにあたる処理をここで行っていたと考えられるから、Zenでも当然こうした配慮はあるものとみられる。また、この中間命令にバッファを組み合わせることで、IntelのDecoded MicroOps Bufferに相当する機能を実装することも容易であろう。

話を戻すと、ZenベースのAMD FXの出荷は2016年末になりそうだが、その前にZenベースのAPUが投入される可能性もないとはいえない。ただそれが2016年前半というのはちょっと考えにくい。恐らくCOMPUTEX前後のタイミングで、まずはZenベースのAMD FXやAPUのシリコンが披露され、2016年後半に製品投入されると考えられる。