Broadcom/TSMC 16FF

BroadcomはVulcanというARMv8-Aベースのコアを開発するという話は2013年に公表されており、2014年には内部構造の概略なども明らかにされた(Photo15)のだが、今回同社は"Optimized Implementation of 3GHz+ ARM CPU Cores in 16nm FinFET Technologies"というタイトルで、このコアの物理実装の話を紹介した(Photo16)。

|

|

Photo15:これは2014年4月のIDC HPC User ForumでBroadcomのEric Hayes氏(VP, Marketing, Infrastructure Networking Group)が公開したスライドから |

|

|

Photo16:左のダイ写真はBroadcomのStrataGXで、これはSingle/Dual Cortex-A9ベースのもので、Vulcanとは何の関係も無い |

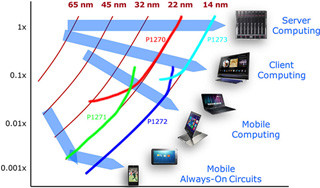

さてそのVulcanの設計目標だが4Pで1.2W~8P 12Wまで。コアあたりにすると0.3W~1.5Wというかなり低い数値となる(Photo17)。BroadcomはARMv8-Aのアーキテクチャライセンスを受けて独自にインプリメントを行っているので、性能/消費電力のカーブは既存のCortex-A57/72などとは異なったものになるが、性能レンジはそのCortex-A72などを上回るところに持ってゆきたいという話となっている(Photo18)。

|

|

Photo17:1.2Wの場合は2GHzを下回る動作周波数なのは間違い無い。表題の3GHzは、ファンはともかくヒートシンクを必要とするような特殊な構成であれば到達できる、というあたりになるのではないかと思う |

|

|

Photo18:Implementationは、既存のASIC向けのStandard Cellをそのまま使ったのでは不十分なので、Semi-Customで行うとのこと。さすがにFull Customは無理だったっぽい |

さて、ここからはインプリメント側の話をいくつか。Photo19はIR Dropを最適化する技法を比較したもので、なるべく精度を高めたほうがIR Dropの無駄なマージンを減らせるという話である。ただ、当然これには時間がかかってしまう。

|

|

Photo19:左はLumped Package(ある程度のブロックをまとめてハンドリング)、右がDetailed Package。回路部位ロックの真ん中あたりのマージンを比較すると右の方がずっと減っていることが分かる |

このIR Dropの設計サイクルをまとめたのがこちら(Photo20)。要するにもうひたすら配置配線以下の作業を繰り返すことで少しづつ最適化を図ってゆこう、という話である。

|

|

Photo20:大まかな配置(Floor Plan)→細かな配置(Place)→クロックツリー生成(CTS)→配線(Route)→設計展開(Extract)→静的タイミング分析(STA)→IR Drop分析(IR analysis)を延々と繰り返すわけだ |

この技法をいきなりVulcanにやるのもアレだと思ったのだろうか、同社はVulcanの物理設計に先立ち、Cortex-A15やCortex-A72を使っての実装のテストを行っていた。Photo21は28nmプロセスを使い、12 TrackのCell LibraryでCortex-A15を実装した結果だが、普通にやると1.5GHzあたりが限界で、その先は消費電力が急増して使い物にならないと判断された。

|

|

Photo21:1.5GHzの時に概ね0.52mW/MHzなので、絶対的な消費電力は0.78Wといったところ。PC用のCPUコアと比較するとかなり低いが、Photo17の設計目標を考えるとこのあたりが限界となる |

ただしそこからClock Treeに繋がるFlipFlopの構造変更(Photo22)やClock Treeそのもののやり直し(Photo23)、L2やRegister Fileなどの手配線による最適化(Photo24)、配置の見直し(Photo25)などを行った事で、エリアサイズを縮小しつつFmaxを向上させることが出来たとする(Photo26)。

|

|

Photo26:T1が最初のデザイン、T3が最終的名デザインである。動的な消費電力(Pdyn)は1.10mW/MHzでそう変わらないが、Clock Treeの最適化などが効果的だったのか動作周波数も1V駆動で2GHzを超え、エリアサイズもやや削減できた |

この知見を元に、Cortex-A72を16FF+で設計したところ、当初の2.5GHz駆動から3GHzまで動作周波数があがり、エリアサイズを7%縮小し、消費電力も0.34W削減できた(Photo27)というのがBroadcomの発表の〆である。

つまり16FF+を使っても、3GHzまでの動作周波数を実現するのは可能であるが、ただしそのためには物理設計の最適化に半年掛かる、という事も明らかになった形だ。大雑把に配置配線→最適化の一巡に2カ月掛かるという話で、これを長いと思うか短いと思うかは難しいところだ。