システムの実装におけるオプション

さまざまなICを搭載するシステム用の基板を実際に設計する際には、恐らく以下のような簡潔な意思決定プロセスに従って、いくつかの重要な対策を講じる必要があります。

- 何種類のクロック周波数が必要であるのかを明確にする

- 基板上の重要なICのタイミング・マージンを評価/特定する

- さまざまなベンダが提供するクロック生成ソリューションについて調査を行い、ジッター、プログラマビリティ、消費電力などの項目を評価する

- 回路基板のレイアウトを行う。クロック経路には細心の注意を払い、クロックの信号品質に影響を及ぼすクロストークなどが生じないようにする

- クロックICのプログラミングを行い、システムの要件に応じて出力レベルや周波数などのチューニングを行う

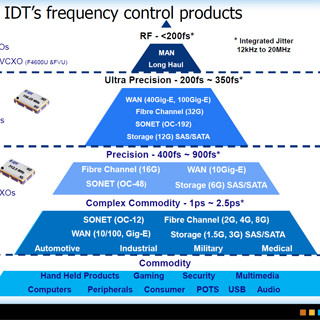

多出力に対応するクロック・ジェネレータは数多く提供されています。そのため、各ICの特性を見極めて、用途に応じた適切な選択を行う必要があります。5P49V5901のRMS位相ジッターの標準値は0.7psで、コア部の消費電力は電源電圧が3.3Vの場合で100mW未満です(図4)。ジッターが小さいため、PCI Express Gen1/2/3、USB 3.0、1/10 Gigabit Ethernetにおけるクロックの要件に対応することができます。

|

|

|

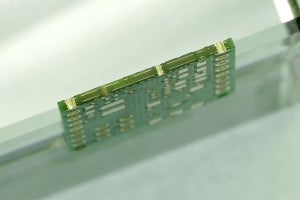

図4 5P49V5901は個別に構成が可能な4系統の差動クロック出力を備えている。高いジッター性能を達成しており、最大350MHzの入出力周波数に対応可能である。オンチップのOTPメモリに、異なる動作モードに対応する複数の構成情報を保存することができる |

VersaClock 5ファミリは、民生用機器、ネットワーク機器、産業用機器、コンピュータ機器、データ通信といった高性能のアプリケーション向けに設計されています。入出力周波数は、最大350MHzまで対応可能です。また、柔軟性に優れていることも特徴の1つです。4系統の独立した汎用差動出力は任意の出力周波数に対応し、LVPECL、LVDS、HCSL、または8系統のLVCMOS出力として構成可能です。さらに、オンチップのOTP(One-Time Programmable)メモリには、4系統の独立した出力に関する複数の構成情報(クロック周波数やI/Oタイプなどの設定)を保存することができます。

2本の選択ピンを備えているので、プロセッサのGPIOまたはブートストラップを使用してアクセスし、最大4種の異なる構成パターンをプログラミングすることができます(1つの構成パターンには、4系統すべてのクロック出力ポートに対するプログラミング・データが含まれます)。4つの異なる構成オプションは、異なる動作モード(全機能の動作、一部の機能の動作、部分的なパワーダウン)、地域(米国、日本、欧州)ごとに異なる規格、システム製造におけるマージン・テストに使用できます。2つのI2Cアドレスのうち1つを使用するように構成し、1つのシステムで複数のデバイスを使用できるようにすることも可能です。

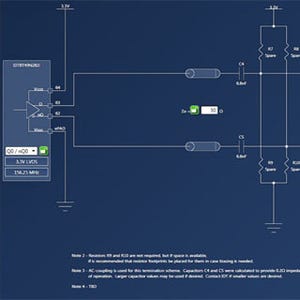

独立したI2Cシリアル・ポートによって新しい構成情報を構成用レジスタに読み込んで、保存済みの設定を上書きしたり、テスト・シーケンスを実行したりすることもできます。各出力の周波数は、単一のリファレンス・クロックまたは水晶振動子を入力として生成します。また、マニュアルによるグリッチレスの切り替えに対応しており、通常動作時に冗長クロック入力のうち1つを選択することが可能です。また、複数のプログラマブル機能を備えるICの構成作業の簡素化に向けたツール「Timing Commander」も提供されています。このソフトウェア・ツールを利用すれば、設計者は直感的に操作が可能で柔軟性に富んだGUIによって、ICの構成/プログラミングが行えます(図5)。

昨今のシステムでは、それぞれが固有のクロック要件を持つ集積度の高い複数のICを搭載するケースが増えています。そうした複雑なシステムで使用する基板を設計する際には、それぞれのタイミング要件を把握することが重要な課題になります。ジッターやデューティ・サイクルなど、それぞれに異なるタイミング上の制約に応じて、各ICにクロック信号を分配しなければなりません。複数のプログラマブル出力を備える最新世代のクロック・ジェネレータは、優れたジッター性能を達成しています。加えて、柔軟性に富んだ構成オプションを備えていることも特徴の1つです。そうした製品を使用すれば、今日のシステムに求められるさまざまなタイミング要件に直ちに対応することができます。また、システムのアップグレードに伴う将来の性能要件にも対応することが可能です。

著者プロフィール

Baljit Chandhoke

IDT

タイミング製品部門 プロダクトライン・マネージャ

2011年よりIDTのタイミング製品部門のプロダクトライン・マネージャとして、新製品の定義、製品ラインの管理やグローバルな顧客の設計課題に対応するインタフェースとしての責任を担っている。

同社入社以前は、2006年~2011年までON Semiconductorの製品マーケティング・マネージャを務め、2003年~2006年までCypress Semiconductorのシニア・アプリケーションエンジニアとして、PLL SerDesやビデオイコライザ製品を担当していた。

インド・ムンバイ大学で電子通信エンジニアリングの学士号、コロラド大学ボールダー校でテレコミュニケーションの理学修士号、アリゾナ州立大学で経営学修士をそれぞれ取得している。