必要な周波数の増加

最近までは、特定の分野を対象とする基板設計者は、5つか6つの異なる周波数に対応するだけで済んでいました。また、基板上の回路が一度起動した後は、周波数は固定でかまいませんでした。例えば、イーサネット用のルーターでは、取り付けられているプラガブル光モジュールの種類に応じて25MHz、125MHz、156.25MHzのうちいずれか1つに対応する回線インタフェースを提供することが求められていました。ところが、今日では1つの分野を対象として設計された機能が直ちにほかの分野にも広まっていきます。現在では、イーサネット用のルーターには、メンテナンス用にUSB 3.0に対応するポートとSDカードのスロットが必要となり、周波数が40MHzと12MHzのクロックも必要となっています。また、OTNに対応するアップリンクのポートもサポートしなければならないケースもあります。このポートでは、ソフトウェアによる構成の変更によって、30~40の異なるクロック周波数のうちいくつかを選択できるようにしなければならない可能性があります。いくつもの異なる周波数が必要になるだけでなく、簡単な整数比では表すことができない周波数も求められるようになっています。

このような問題は、柔軟性が高く、単一のデバイスに複数のPLLを搭載しているタイミング製品を採用することによって解決できます。ただし、柔軟性が高くなると、プログラミングの複雑さが増大します。このような新たな製品については、IDTの「Timing Commander」のような構成ツールを提供する必要があります。Timing Commanderを使用すれば、複雑なデバイスの設定を容易に行うことができます。必要な入力周波数/出力周波数をツールに入力するだけで、すべてのレジスタをどのようにプログラムすればよいかを知ることが可能です。また、各周波数プランに対応する運用ソフトウェア向けの出力ファイルや、デバイスに対して永続的な設定を行うための出力ファイルも提供してくれます。

周波数領域ジッター

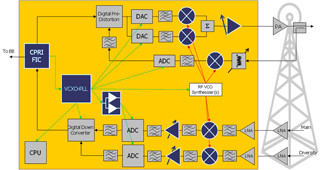

周波数領域ジッター(Frequency-domain Jitter)とは、望ましくない余計な周波数成分のことです。このジッターは、実世界のあらゆるクロック信号に含まれています。一般に、周波数領域ジッターは、所望の周波数(搬送波)からの周波数オフセットに対して、搬送波のエネルギーを基準とした1Hz帯域幅の相対エネルギーをプロットしたグラフで表現されます。この不要な周波数成分が高性能のA/Dコンバータ(ADC)やD/Aコンバータ(DAC)のリファレンス・クロックに存在する場合、特に大きな問題になります。ADC/DACが、望ましくない周波数のエイリアスを多数生成してしまうからです。また、高速シリアルインタフェースの物理層(PHY)デバイスは、通常、ADCやDACを備えています。そのため、この用途でも周波数領域ジッターが大きな問題になる可能性があります。

高性能のアプリケーションでは、タイミング・デバイスが駆動するデバイスの入力仕様とタイミング・デバイスの位相ノイズ性能を比較する必要があります。位相ノイズ性能は、タイミング・デバイスの実際の構成に依存しますが、優れた構成ツールであれば、各構成における値をグラフで示してくれます(図1)。

信号のプロトコル、電圧のシフト、電源のフィルタリング

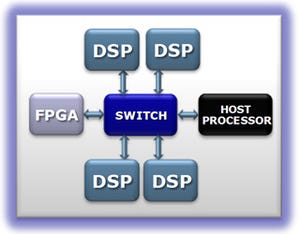

基板を設計する際、クロック・ツリーには、ほとんどの基板サブシステムに実装されるデバイスと、水晶振動子や発振器などの周波数リソースが接続されます。そのため、通常は、シングルエンド・プロトコル(CMOSなど)と1つ以上の差動プロトコル(LVDSなど)の間での信号変換と電圧振幅の調整が必要になります。一般に、そうした処理は受動部品で構成した回路で行いますが、能動型のレベル・シフターが使用されることもあります。各プロトコルの電圧/電流の仕様に精通していない設計者がこれを行うには、数多くのアプリケーション・ノートを参照しなければなりませんでした。それに対し、構成ツールを使用すれば、特定のタイミング・デバイスの入力/出力プロトコルや電圧の不整合に対処する方法を知ることができます(図2)。

また構成ツールの機能を使用することにより、特に高性能のデバイスで必要になる電源フィルタやループ・フィルタについても、推奨回路図や各部品の値を生成することが可能です。

冗長性と障害対応

現在、人々の生活はますますネットワーク接続への依存度を高めています。そのため、携帯型の端末からテラビット級のコア・ルーターに至るあらゆる機器で、高い信頼性で動作することがより重要になっています。また、音声電話用のスイッチや軍用グレードのフォルトトレラント・システム向けに考案された手法が、ネットワーク・レイヤーの下層にまで適用されるようになっています。現在では、すべてのシステムを、故障率(FIT)を可能な限り低減し、障害が発生した際の影響を最小化(グレイスフル・デグラデーション)するように設計しなければなりません。多くのシステムは、障害が発生した際の動作についてITU-T G.8261などの国際規格に準拠する必要もあります。

タイミング・デバイスでは、こうしたニーズに対応するための主要な機能として、スイッチオーバーとホールドオーバーが用意されています。スイッチオーバーとは、1つのクロック源について、信号品質の低下や信号の完全な喪失が検出された場合に、バックアップ用のクロック源に切り替える処理のことです。一方のホールドオーバーは、スイッチオーバーが行えなかった場合に実行する処理です。ホールドオーバーでは、バックアップ用のすべてのクロック源が不適合である場合に、一定のレベルの機能を維持するために局所的な水晶振動子や水晶発振器を代替として使用します。

信頼性の高いクロック・ツリーを構築することは、システム・レベルの問題です。言い換えれば、この問題はクロック・ツリー全体のレベルで解決する必要があります。外部で定義されたシステム・レベルの仕様を満たさなければならない場合には特にそうです。この作業には、やはり豊富な知識を持つ技術者が必要です。タイミング・デバイスのメーカーには、システムについて熟知した経験豊富なアプリケーション・エンジニアリング・チームが編成されています。基板設計者はそのチームと連携する必要があります。これは、デバイスごとに簡単に解決できる類の問題ではありません。異なるメーカーの製品を組み合わせようとしたことがある人ならば、このことに共感していただけるでしょう。

まとめ

基板の設計は、デジタル、アナログ、ソフトウェア、熱設計、機械設計といった多様な分野にわたる深い知識を必要とする難しい仕事です。クロックの分野では、この5年間で必要な周波数の数が急激に増加し、時間領域/周波数領域のジッターに対する要件が厳しくなっています。加えて、異なる多くの信号プロトコルと電圧のレベルが混在するようになりました。タイミング・デバイスの主要なメーカーは、こうした問題について認識しており、各種のツールを提供することで対応を図っています。そうしたツールとしては、豊富な機能を備えつつユーザーが使いやすいクロック・ツリー生成ツール、パラメータ検索ツール、構成ツールなどがあります。これらのツールは、基板設計者にとって貴重な支援を提供してくれるものですが、その負担のすべてを取り去ることはできません。ツールを活用しても解決できない問題については、豊富な知識を持ち、クロック・ツリーがシステムに与える影響を十分に理解しているアプリケーション・エンジニアリング・チームからのサポートを受ける必要があります。ツールやアプリケーションに関する専門知識を提供しているタイミング・デバイスのメーカーと連携すれば、基板設計者の負担は軽減され、その努力が成功につながる確率も高まるはずです。

著者紹介

Ian Dobson(イアン・ドブソン)

IDT タイミングおよび同期製品部門 システムアーキテクチャ ディレクタ

IDTにて、顧客のシステムを理解し、現行および新規のIDT製品がいかに顧客のニーズに対処できるかを識別する役割を担当。

IDTに入社する前は、キャリアの大半を電気通信業界に置き、ASICやボードやシステムレベルの製品開発に従事。

Alcatelでのハードウェア開発やNewbridge Networks CorpやTundora Semiconductorにおけるシニアポジションも務める。