I-TLB(グラフ43~48)

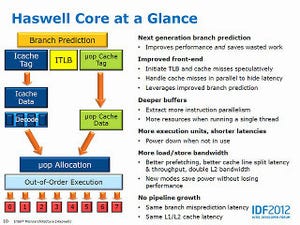

I-Cacheのテストも一通り終わったので、次はTLBを見てみたい。HaswellのTLBの構成は、こちらの35ページ(2.1.4 Cacge and Memory SubsystemのTable 2-4)にある通りである。I-TLBの場合、4KB Pageだと128 Entry/4-way set assosiativity/2 Threadで、2MB/4MB Pageでは8 Entry/Threadとなっている。L2はI-TLB/D-TLBの共用で、1024 Entry/8-way Set Associativityである。Ivy BridgeはL1 I-TLBは128 Entryと同じだが、L2 TLBは512 Enrtyである。この違いが結果に露骨に出ている感じがある。

まずグラフ43はNear Jump/Forwardである。Segment Countが128あたりまではL1 I-TLBにHitしている関係でどちらも非常に高速だが、これを超えるとL2 TLBにアクセスとなる。Ivy Bridgeでは512÷2=256 Entryあたりから急速にLatencyが増えているが、Haswellでは1024÷2=512 Entryあたりまで綺麗にフラットを維持しており、しかもその際のLatencyも低い。L2 TLB MissになるとMemory Access(というか、L2 Cache/L3 Cache Access)となる関係で相応にLatencyが増えているが、これは同程度である。

この傾向はBackward(グラフ44)やRandom(グラフ45)でも同じだが、強いて言えばL2/L3 Cacheアクセス時にはHaswellの方がややLatencyが増えているのは面白い。

Far Jump(グラフ46~48)も傾向は同じで、ただしこちらの方がL2 TLB Miss時のHaswellのLatencyが更に増えているのはちょっと興味深いところ。TLBのCachingは、HaswellのL2/L3 Cacheにとってはややイレギュラーな扱い、という事に見える。