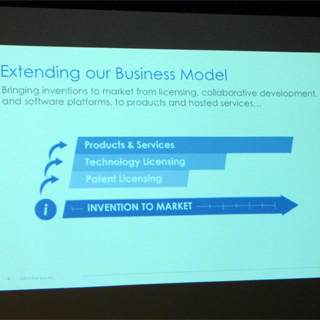

R+ Enhanced Standard Solutions

「R+ Enhanced Standard Solutions」は2013年1月に発表されたものである(Photo11)。今回説明されたR+ LPDDR3は、この新しいメモリインタフェース向けソリューションの最初のものと考えればよい。

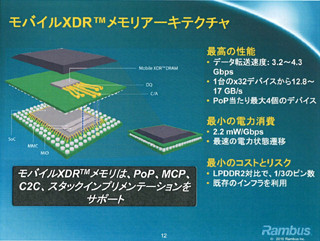

ご存知の通り、RAMBUSはこれまで一貫して「独自の高性能なメモリシステムを提供する」という位置づけを崩さなかった。この方針が若干崩れてきたのが2011年に発表したマルチモードメモリコントローラで、XDR/XDR2とDDR3/GDDR5に対応するという仕組みだ。FlexModeという仕組みでピン配置を多重化することで、パッケージを変えずに複数のメモリに対応できるという仕組みを提供したのだが、マルチモードメモリコントローラはともかく今のところXDR2メモリの採用事例は皆無である。

実は2012年秋のIDFでRAMBUSはXDR2を使ったDIMMを試作したり(Photo12)、これを利用した基板デモを行なったり(Photo13)したものの、インパクトは無かったようだ。

|

|

|

|

Photo12:これは同社がDynamic Point-to-Pointと呼んでいた、XDR/XDR2をベースに2枚刺しのDIMMスロットをサポートする配線方法のデモ |

Photo13:LPDDR4との互換性の話は次のスライドで |

最大の問題は、XDR2がPrimary Targetとして考えていたGDDR5の後継が結局HMC(Hybrid Memory Cube)になってしまったからだ。正確に言えば、AMD、Intel、NVIDIAというGPUベンダ3社(Intelの場合はGPUというよりはGPGPUだが)を除く主要なベンダはHMC Consortiumに加盟してしまっており、またJEDECもこの動きを事実上追認している(JEDECではGDDR5の後継規格策定の作業を行なっておらず、またWorkshopなどではJEDECメンバーが相次いでGDDR5の後継はHMCになると発言している)から、よほどの事が無い限りこの趨勢が覆ることはなさそうだ。

結局のところXDRはともかく、XDR2(初代)~TBI~XDR2(TBIの仕様を含んだ改訂版)という一連の高速メモリI/F開発の投資は丸々無駄になってしまった、というと大げさかもしれないが、回収は非常に難しそうな趨勢だ。こうした投資の失敗は、現在のRAMBUSの方針には合わないということだろう。

R+ LPDDR3の特徴は、LPDDR3モードとR+LPDDR3モード、そしてLPDDR4モードの3種類を持つことである(Photo13)。このR+LPDDR3モードの中身は後述するとして、I/Fは共用できる上に消費電力は下がり、50%増しの帯域を確保できるというのがメリットとして挙げられている。「で、どのメモリベンダがR+LPDDR3 DRAMを製造するのか?」と確認したところ「具体的には言えないが、すでに協力体制はある」という説明が返ってきた。

|

|

|

Photo14:2種類の規格の違い。DQのNGSというのは、RAMBUSが提供する電圧0.5VのNear Ground Signalingという伝送方法 |

ではそのR+LPDDR3とは何か? というのがこちらである。元々LPDDR3とLPDDR4では、配線にかなりの違いがある。これはDDR3とDDR4も同じであり、結果としてどのメーカーもLPDDR3→LPDDR4の移行に際してはメモリコントローラ周りは完全に作り直しになる。これに目をつけて、R+LPDDR3では一部LPDDR4の規格(特にDQ)を先取りする形で実装している。面白いのはR+LPDDR3は、LPDDR4が投入されるまでの「中継ぎ」と割り切っており、特にコントローラ側の設計変更が一切無しでいける様にしているのが特徴である。もちろんメモリチップや基板デザインなどは変更になるが、これはSoCの開発コストに比べればずっと少ない。なので、LPDDR4が広く利用できるようになったらそちらに切り替えることを前提に、それまでの中継ぎソリューションとして提供していることだ。こうした方向性は、これまでのRAMBUSでは考えられないものだったと思う。