より高性能な製造プロセスを利用するTegra 4i

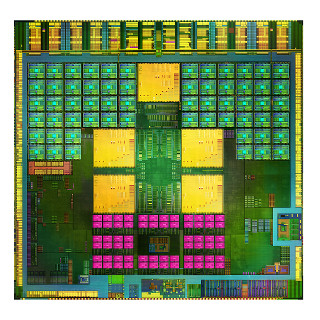

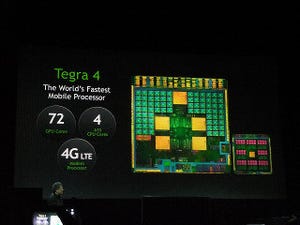

一方、Tegra 4ファミリーのエントリーモデルとなる「Tegra 4i」は、Icera 500ソフトウェアモデムのベースバンドプロセッサを統合するとともに、CPUコアにCortex-A9 r4を採用し、60コアのグラフィックス機能を搭載していることは、既報のとおりだ。ただし、この60コアのグラフィックス機能の構成は、業界関係者からのリーク情報も踏まえてピクセルシェーダーが40コア、バーテックスシェーダーが20コアという構成だと類推したが、実際には、

3 VPE:12コア

2 ピクセルシェーダーパイプ:48コア

という構成を採ることが明らかにされた。2ピクセルシェーダーパイプで48コアを統合ということからも分かるとおり、Tegra 4iでは「ダイサイズを小さく収めるために、メモリインターフェースをシングルチャネルに留める必要があったため、ピクセルシェーダーパイプの構造を変更している」と、同社でグラフィックスアーキテクチャの開発などを統括するトニー・タマシ上級副社長は説明。そのピクセルシェーダーパイプの構成はTegra 4の3組のALU構成から、6組のALUでテクスチャフィルタリングユニットやテクスチャL1キャッシュを束ねる形に変更されている。その一方で、Tegra 4iの"上位モデル"では、より高速なDDR3L-2133をサポートすることでメモリ帯域を稼ぎ、Tegra 3の5倍となるグラフィックスコアを効率よく利用できるようにしている。

さらに、NVIDIAはTegra 4が28nm省電力デバイス向けプロセス「CLN28HPL」を採用しているのに対し、Tegra 4iについては昨年後半より本格的に稼働しはじめた高性能モバイル機器向けプロセスの「CLN28HPM」を採用していることを明らかにした。CLN28HPMは、省電力デバイス向けとパフォーマンスデバイス向けプロセスの中間に位置づけられる製造プロセスで、リーク電流はCLN28HPLよりも多くなるが、CPUコアやグラフィックスコアをより高速に動作させることで、Tegra 3に比べて大幅なパフォーマンスアップを実現している。

| ■Tegra 4シリーズの仕様詳細 | |||

| Tegra 4 | Tegra 4i | Tegra 3 | |

|---|---|---|---|

| 開発コード名 | Wyane | Grey | Kal-El |

| 製造プロセス | 28nm CLN28HPL |

28nm CLN28HPM |

40nm CLN40LPG |

| CPUコア | ARM Cortex-A15 | ARM Cortex-A9 r4 | ARM Cortex-A9 |

| コア数 | 4+1 | 4+1 | 4+1 |

| CPUクロック(最大) | 1.9GHz | 2.3GHz | 1.7GHz |

| L1キャッシュ(命令L1/データL1) | コアあたり32KB/32KB | コアあたり32KB/32KB | コアあたり32KB/32KB |

| L2キャッシュ | 2MB共有キャッシュ および512KB(+1コア専用) |

1MB | 1MB |

| GPUコア | 72 | 60 | 12 |

| Vertex Shader | 24 | 12 | 4 |

| Pixel Shader | 48 | 48 | 8 |

| GPUクロック(最大) | 672MHz | 660MHz | 520MHz |

| メモリ | DDR3L & LPDDR3 | LPDDR3 | DDR3L & LPDDR2 |

| メモリチャネル | デュアル | シングル | シングル |

| メモリクロック(最大) | DDR3L/LPDDR3-1866 | LPDDR3-2133 | DDR3L-1500 |

| 最大メモリ容量 | 4GB | 2GB | 2GB |

| LCDパネル出力(最大) | 3200×2000ピクセル | 1920×1200ピクセル | 2048×1536ピクセル |

| HDMI | 4K(UltraHD) | 1080p | 1080p |

| ベースバンドプロセッサ | オプション | NVIDIA i500内蔵 | オプション |

| パッケージサイズ | 23×23mm BGA 14×14mm FCCSP |

12×12mm POP 12×12mm FCCSP |

24.5×24.5mm BGA 14×14mm FCCSP |

次ページ:GPUの並列処理性能を活かす新技術を開発