大きく変わったグラフィックス機能

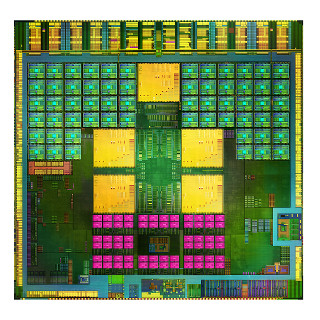

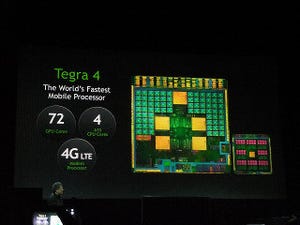

当初、Tegra 4ファミリーに搭載されたグラフィックス機能は、Tegra 3に搭載された「ULP GeForce」の改良版と見られてきた。しかし、今回公開された技術資料からは、NVIDIAがTegra 4ファミリーの開発において、グラフィックスコアの省電力性を高めるとともに、より少ないトランジスタサイズを実現すべく、グラフィックスアーキテクチャにも大きなメスを入れていることが明らかになった。

Tegra 4のグラフィックス機能は、4つの積和算ユニットを1組とするALU(Arithmetic Logic Unit)を最小単位に、Vertex Shaderの役割を果たすVPE(Vertex Processing Engine)と呼ぶVec4 ALUを6基と、4つの積和算ユニットを1組とするALUを3つ束ね、テクスチャユニットやL1キャッシュを組み合わせたピクセルシェーダーパイプを4基搭載。つまり、

6 VPE:24コア

4 ピクセルシェーダーパイプ:48コア

という構成を採っている。

このピクセルシェーダーパイプは、従来のSIMD(Single Instruction, Multiple Data)方式から、新たに複数の命令をひとまとめにして処理することができるVLIW(Very Long Instraction Words)方式対応となり、より効率的に複数のコアを利用できるようにしている。

さらにこのピクセルパイプには16bit浮動小数点テクスチャフィルタリングユニットとテクスチャL1キャッシュが組み合わされるほか、4つのピクセルシェーダーパイプで共有するテクスチャL2キャッシュが追加され、HDR(High Dynamic Range:ハイ・ダイナミック・レンジ)テクスチャ処理や、Tegra 4の新機能として追加されたComputational Photograph Architecture「Chimera」のHDR写真・ビデオ合成などにも利用される。

もう一つ、Tegra 4ファミリーのグラフィックス機能で特筆すべき点は、そのダイサイズに占めるGPUコア面積に小ささだ。NVIDIAが公開した資料によれば、Tegra 4のGPUエリアは10.5平方mmと、iPhone 5に採用されているA5xの26.2平方mmと比べると半分以下しかないにもかかわらず、約3倍の演算性能を実現していることが示された。このため、Tegra 4ではOpenGL ES 3.0への対応で不可欠となる32bit浮動小数点精度のピクセルレンダリングはサポートせず、20bit精度に留めるなど、省電力性やトランジスタ数を削ることを最優先している部分がある。その詳細については、改めてレポートする。