ARM Techcon 2012の内容から、前回のCortex-A53の解説に引き続き、予告したとおり、今回はCortex-A57のレポートをお届けしたいと思う。

Cortex-A57(以下A57と略す。Photo01)は、64bitアーキテクチャを含むARMv8に対応するアウトオブオーダー機構を持つプロセッサである。1.7GHz動作時に現行のCortex-A9(1.4GHz)の3倍程度、A15(1.5GHz)の1.3倍程度の性能を持つことになるという(Photo02)。

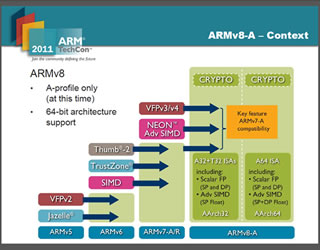

ARMv8には、従来のARMv7互換のAArch32と新規に追加されたAArch64の2つのアーキテクチャ、命令セットがある。しかし、A57は、1つのパイプラインで2つのアーキテクチャを実行する。というのも、AArch64の命令体系は単純化されており、条件付き実行機能(ARMアーキテクチャでは、命令内に条件指定ビットがあり、演算結果により、後続の命令をスキップできる)などの複雑な機能がなく、デコーダーなどの実行部分の負担は、かえって小さい。ただし、命令長や対象データが64bitになっているため、パス幅が増えており、これが集積度などに影響する。

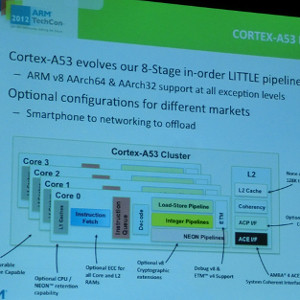

A57は、アウトオブオーダー機構により、高い実行性能を持つが、その分消費電力も大きい。こうした問題に対し、ARM社は、性能はさほど高くないが、消費電力の小さなARMv8プロセッサであるA53を開発。この2つを組み合わせ、低~中負荷時にはA53で実行し、高負荷時にはA57を使う、big.LITTLEコンピューティングを提唱している(Photo03)。この技術を使うことで平均の消費電力を下げることが可能になっている。ARM社の資料によれば、20nmで製造されるA57/A53のデュアルコアのbig.LITTLE構成では、32nmのクワッドコアCortex-A9の2.6倍以上の性能を出しながら、消費電力はかえって低くなっているという(Photo04)。

A57は、最大4コアのクラスタを構成し、4クラスタを接続することで最大16コア構成が可能になる(Photo05)。また、A53のクラスタ(最大4コア)と接続することも可能だ。L2キャッシュは、クラスタ内で共有し、設計時には512K/1M/2Mの3種類の構成が選択できる。L1キャッシュのサイズは固定で、命令キャッシュが48キロバイト、データキャッシュが32キロバイトである。また、

ARMv8では、ARMv7までオプションであったSIMD演算機構であるNEONが標準となった。このため、SIMDや浮動小数点演算部分も実行パイプに完全に組み込まれている。このA57は、最近設計されたものであるため、モバイルやネットワーク処理、サーバといったワークロードを念頭において設計されたという。サーバなどのミッションクリティカルな用途のため、L2キャッシュは、SEC-DED(Single Error Correction - Double Error Detection。1ビットエラー修正、2ビットエラー検出)方式のECCを備え、L1キャッシュにはパリティビットがある。また、エラー検出とハンドリングを可能にするRAS機能も搭載しているという。

A57は、28nmプロセス以降での製造を想定しており、20nmプロセス時に最大クロック周波数が1.5~2.5GHzとなる。ただし、モバイル向けに電力効率が最大になるのは、28nmプロセスだという。

次ページ:Cortex-A57の詳細