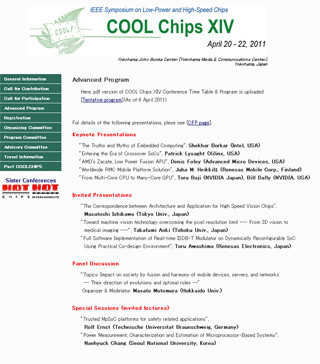

2011年4月20日から22日の3日間、横浜の情報文化センターでCOOL Chips XIVが開催された。今年は福島の原発事故の影響で海外からの参加者が減少したが、国内の参加者は増えて全体としては180人あまりが参加し、前年(2010年)の参加者数を上回った。

今年は2件の特別講義、5件の基調講演、3件の招待講演が行われ、研究成果の発表としては10件の論文発表と19件のポスター発表が行われた。しかし、特別講義や一部の基調講演では講演者は来日せず、TV会議システムを使った講演となった。

省電力の再構成可能プロセサの研究

COOL Chipsはもともと省電力を標榜するコンファレンスであるが、今年はアーキテクチャ的な工夫でローパワーを強調する発表が多かった。クロックゲートやパワーゲートはすでに一般的になっており、さらに消費電力を減らすアーキテクチャやスキームを追求するという方向に研究の重点が向かっている。その1つの方向として再構成可能なプロセサがあり、今回のCOOL Chipsでは東芝のFlexGripと慶応義塾大学のSLD-1というプロセサが発表された。

|

|

|

|

FlexGripについて発表する東芝のYoshikawa氏(左)とSLD-1を発表する慶応義塾大学のOzaki氏(右) |

|

並列性の高い問題はマルチコアCPUやGPUで効率よく処理できるが、順次処理が必要な問題も多くあり、これらはマルチコアやGPUではうまく処理できない。FlexGripは、この順次処理の処理効率を高めようというアプローチのアーキテクチャのプロセサである。FlexGripは次の図のような構成になっており、ホストコントローラから仕事を受けるアクセラレータという位置づけになっている。この図のように、FlexGripは分岐ユニット(BU)と2つの演算ユニット(EU)と2つのロードストアユニット(LSU)を持っている。

Out-of-Order処理を行うスーパスカラプロセサでも命令レベルの並列性を見つけ出して並列に実行するが、FlexGripの分岐ユニットは2つの演算ユニットと2つのロードストアユニットに実行すべき命令ブロックのアドレスを指示し、各実行ユニットはそれぞれに割り当てられた命令を独立に実行していくという形で命令の並列実行を行っている。ただし、データ依存性がある場合にはハードウェアが待ち合わせを行う構造になっている。

そして特徴的なのが、次の図に示す演算ユニットのファンクションブロックである。

16ビット演算の場合は2系列、32ビット演算の場合に1系列のデータに対して、AND、OR、NAND、XORなどの論理演算と加減算などの算術演算のペアを2回実行できるようになっている。また,後段のペアには前段の演算結果だけでなく,レジスタからの別のオペランドを入力することができる。

チップには2個のEUが搭載され、各EUには4個のファンクションブロックがあるので、32ビットデータの場合、毎サイクル各16回の論理演算と算術演算が実行できる。ということで,Out-of-Orderのような複雑な制御を行うことなく命令の並列実行を可能とし、シーケンシャルな論理-算術-論理-算術演算を1サイクルで処理できるファンクションブロックで高い演算密度を実現することにより高い電力性能比を実現している。このファンクションブロックの機能は各演算の種別とスイッチの切り替えを行うVLIW命令で制御されており、ある意味では、サイクルごとに再構成を行う演算器とみることができる。

このチップは359Kgateの規模で、40nmプロセスで作られ、333MHzクロックで動作し78.3mWの消費電力と発表された。

慶応義塾大学と東京大学、東京農工大学、電気通信大学、芝浦工業大学のチームのSLD-1はより強力な演算器のネットワークを持つ再構成可能なプロセサである。従来、再構成可能なプロセサでは処理のフェーズに応じて構成を変えることにより、小さなハードウェアで効率的にアクセラレーションを行うというものが多かったが、この方式では構成を変えるために使われるエネルギーが全消費電力の1/4程度を占めるという。そこで、処理のフェーズごとに構成を変えるのではなく、全てのフェーズに必要なデータパスをあらかじめ作っておき、処理中には再構成を行わないようにして低電力を実現しようというのがSilent Large Datapath(SLD)プロセサの考え方である。

このためSLD-1は8×8という大量のPE(Processing Element)のアレイを持っている。そして、各PEは上下、左右の隣接したPEとのデータのやり取りと斜め右上のPEにデータが送れるようになっている。各PEは24ビット幅のALUと隣接PEとの接続を行うクロスバを持っている。

そしてBlack Diamondという名前のコンパイラを開発しており、Cに類似した言語で書いたプログラムをこのPEアレイにマッピングすることができるようになっている。このような大量のPEアレイをどの程度有効に使えるのかは処理する問題によるが、64PEのうちの60PEを使用できるという例も報告された。

SLD-1は65nmプロセスで作られ、チップサイズは4.2mm×2.1mmとなっている。電源電圧1.2V、210MHzクロックで動作させた場合の消費電力は16mW強である。

FlexGripやSLD-1の考え方が今後の主流となるかどうかはまだ分からないが、根本的なアーキテクチャから順次処理の効率改善や、再構成エネルギーの削減を目指すというアプローチは注目に値する。電源電圧が下げられなくなりクロックの向上による性能改善が止まったことから、このようなアーキテクチャによる性能改善やエネルギー効率の改善が重要性を増してきている。