改良されたデザインフロー

デザインフローについてはタイミング解析、シミュレーション・エクスポート、及びTclスクリプティングの3つの主要な改良が施されました。

新しいタイミング解析(Timing Analysis)ビューは、タイミング情報を閲覧するための、使いやすさにこだわったグラフィカル環境です。設計制約を選択すると、タイミングパス、詳細パス、及びパスのスケマティック・ビューが表示されます。新しいタイミング解析ビューの主な利点は、タイミングに関する設計制約を変更できることであり、インプリメンテーションを更新することなく解析を再実行できます。大規模のデザインの場合、この機能は各タイミング解析の時間を節約します。

もう1つの改良点は、新しいシミュレーション・ウィザード(Simulation Wizard)により、デザインをシミュレータにエクスポートできることです。シミュレーション・ウィザードは、必要な手順を通じてユーザをガイドし、RTLやゲートレベルなどを必要なフォーマットで、デザインをシミュレータにエクスポートできるようにします。

Diamondソフトウェアは、デザインフローをスクリプト処理するための新しい機能を加えています。Diamond固有のTclコマンド・ディクショナリが、プロジェクト、ネットリスト、HDLコードチェック、電力計算、及びハードウェアデバッガの挿入と解析用に用意されています。Diamond環境のTclコンソールに加え、独立したTclコンソール・アプリケーションにより、GUIと無関係にスクリプトを実行できます。さらに以下の例に示すように、正しくセットアップが完了した後は、DOSまたはその他のコマンドシェルでTclスクリプトをコマンドとして直接実行できます。

まとめ

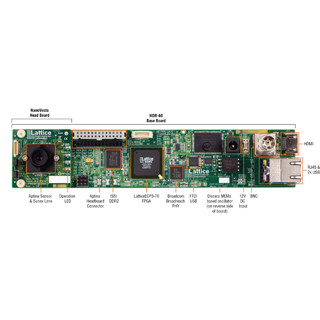

FPGAは様々なアプリケーションやタスクに使用されるようになっているため、デザインの実装方法を推敲する能力が重要なポイントになります。次世代の設計ツールは、まさにこれを成し遂げ、特にLattice Diamondの設計環境は、現在のFPGA設計における課題に対処した最初の製品です。Diamondはデザインの推敲、使いやすさ、改良されたデザインフロー、及びその他様々な機能が強化されています。新機能と強化機能の組み合わせにより、ユーザは迅速かつ容易に設計をおこない、最良の結果を導き出すことができます。

Lattice DiamondはWindows版及びLinux版ともに、LatticeのWebサイトからダウンロードできます。インストール後は、無償ライセンスまたは有償(サブスクリプション)ライセンスのいずれかで使用できます。

無償ライセンスは、MachXOやLatticeECP2など、広く採用されている多くのLatticeのデバイスにアクセスできます。有償ライセンスは最新のLatticeECP3デバイスを含む、全てのLatticeのFPGAに対応します。両ライセンスともにSynopsysのSynplify Pro for Lattice論理合成ツールと、AldecのActive-HDL Lattice Edition II混在言語対応シミュレータが統合されています。

筆者紹介

Brian Caslis

Lattice Semiconductor,Senior Software Product Planning Engineer