COOL Chips XIIIにおいて、IBMのKahle氏に続いて富士通の山崎氏が日本の次世代スパコンのエンジンとして使われるSPARC64 VIIIfxプロセサに関して基調講演を行った。

|

|

|

図1 SPARC64 VIIIfxに関する基調講演を行う富士通の山崎氏 |

SPARC64 VIIIfxはSPARC V9命令仕様に準拠するプロセサであるが、このプロセサではHPC-ACE(High Performance Computing - Arithmetic Computational Extensions)と呼ぶ独自のアーキテクチャ拡張を行っている。その名の通り、科学技術計算向けの演算性能の向上を狙った拡張であるが、この命名にはHPCの世界でエースになるという意気込みが込められているという。

図2に示すように、HPC-ACEでは倍精度浮動小数点レジスタ数を従来の32から256へと大幅に拡張している。少し小さくて見難いが、下側の図が拡張の効果を示している。レジスタ数が少ないと左側のようにループ0が終わってからループ1の実行を始めるというように処理を進めざるを得ないが、十分にレジスタがあると右側のように複数のループを少しずらせて並列に実行することが可能になる。

当然であるが、直前の演算の結果を使って次の演算を行う場合には、前の演算が終わって結果が出るまで次の演算は開始できない。浮動小数点演算は5~6サイクルを必要とするので、 このような場合には演算完了待ちの空きサイクルが出てしまう。しかし、右側の図のようにすると、ループ0の演算命令、ループ1の演算命令、…と順に実行して、その後、ループ0の直前の演算結果を使う演算命令、…という風にソフトウェアパイプラインで実行すれば、各ループの前の演算命令とその結果を使う演算命令の間を他のループの命令で埋めることができる。

SPARC64では毎サイクル2個の浮動小数点演算命令を発行できるので、仮に5サイクルの空きを埋めようとすると10命令必要となり、ループ10回分を重ねて実行することが必要となる。つまり、ループ1回分の実行に必要となるレジスタ数の10倍のレジスタが無いとこのような実行は出来ないことになる。

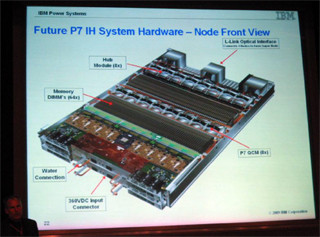

なお、POWER7でも従来の32レジスタから128レジスタに浮動小数点レジスタを拡張しており、両者の目指す方向はかなり一致している。

また、HPC-ACEの第2の拡張は演算機能の強化であり、POWER7と同様に1サイクルに8演算を実行するという拡張を行っている。従来のSPARC64プロセサでは倍精度浮動小数点の積和演算を行うユニットを2個備えていたが、HPC-ACEでは、それぞれのユニットの積和演算器を1個から2個に倍増している。そして、1つの演算ユニットの中の2つの演算器は同じ命令で動作するという2並列のSIMD方式である。これはIntelのSSE2で64ビットの倍精度浮動小数点演算を2並列で実行できるというのと同様の方式である。

さらに、新しい演算命令として逆数の近似値生成命令、三角関数、最大値、最小値命令を追加し、マスクを使ってSIMD命令の個々の演算器の動作を制御する機能を追加している。