2023年6月に京都で開催される「2023 Symposium on Technology and Circuits」の主催者が回路設計分野の注目論文を紹介している。その中で、今回はデジタル回路、クロック回路、ワイヤライン分野の注目論文を紹介する。

デジタル回路設計:FPGAやDSPチップレットなどを集積したヘテロジニアスSiPをミシガン大が報告

- Arvon: A Heterogeneous SiP Integrating a 14nm FPGA and Two 22nm 1.8TFLOPS/W DSPs with 1.7Tbps/mm2 AIB 2.0 Interface to Provide Versatile Workload Acceleration (論文番号:C7-1)

多彩なワークロードアクセラレーションを実現するためには、複数のチップレットと高性能インタフェースの高度な集積が必要であるが、ミシガン大学はIntelと共同で、Intel独自のEmbedded Multi-die Interconnect Bridges(EMIB)を活用して、2つの22nm DSPチップレットと14nm FPGAチップレットを集積したヘテロジニアスSiPを開発したことを報告する予定。

チップレットはAdvanced Interface Bus(AIB)1.0インタフェースとAIB 2.0インタフェースを介して通信し、36μmピッチ・マイクロバンプを用いてAIB 2.0 I/Oプロトタイプを実証し、0.10pJ/b(アダプタを含む場合0.46pJ/b)で4Gbps/pinを達成したという。このSiPはプログラマブルで、ニューラルネットワークから通信処理までのワークロードをサポートし、4.14TFLOPS(FP16)のピークパフォーマンスを実現。パフォーマンスと利用率を最適化するため、FPGAとDSPを横断するワークロードをマッピングするコンパイルフローも提供している。

クロック回路設計:低ジッタかつ高出力周波数のクロック逓倍回路をKAISTが開発

- A 122fsrms-Jitter and –60dBc-Reference-Spur 12.24GHz MDLL with a 102-Multiplication Factor Using a Power-Gating Technique (論文番号:C26-5)

リングオシレータ型のインジェクションロッククロック逓倍器は、低ジッタ出力クロックの生成に適しており、シリコン面積を最小限に抑えることができるが、出力周波数を上げにくい欠点があった。

そこで、韓国科学技術院(KAIST)は、低ジッタかつ12.24GHzの出力が可能なクロック逓倍回路を開発したことを報告する予定。リングオシレータ型の発振器を用いることで0.066mm2の省面積化を達成したという。また、リングオシレータ型の周波数を上げにくい欠点は、ゲーティング技術の提案により出力クロックの高周波数化を実現したとしているほか、内蔵する校正回路により、クロック起因のスプリアスを-60dBcまで低減することに成功したともしている。

シリコンフォトニック回路設計:異種材料集積シリコンフォトニック・トランシーバをIntelが開発

- A 256 Gbps Heterogeneously Integrated Silicon Photonic Microring-Based DWDM Receiver Suitable for In-Package Optical I/O (論文番号:C6-2)

インパッケージ・シリコンフォトニック・トランシーバは、データセンターの相互接続における帯域幅のボトルネックを緩和し、これからの人工知能や機械学習のワークロードに対する性能要求を満たすことができると期待されており、Intelは今回、異種材料集積シリコンフォトニックマイクロリングベース高密度波長分割多重受信機を提案する予定としている。

ディザベース熱制御ユニットが光デマルチプレクサ内のマイクロリング共振器をレーザー格子に対してサブピコメートルの分解能で調整し、送受信機はシリコン光IC上に28nm CMOSプロセスの電子ICとして積層実装。等しい200GHz間隔の8波長を利用することで、データレート256GbpsでBER<1e-12、光パワー3.6dBm、エネルギー効率3.8pJ/bを達成したという。

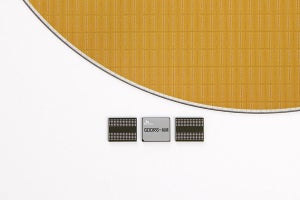

マシンラーニング回路設計:3D NANDを使ったインメモリ検索チップをMacronixが発表

- Chip Demonstration of a High-Density (43Gb) and High-Search-Bandwidth (300Gb/s) 3D NAND Based In-Memory Search Accelerator for Ternary Content Addressable Memory (TCAM) and Proximity Search of Hamming Distance (論文番号:T15-1)

台Macronix Internationalは、96層3D NANDを使った高密度(43Gb)なインメモリ検索チップを発表する予定。String-select lineと呼ぶ新しい回路設計により、400mW以下の消費電力で最大300Gbpsのバンド幅を達成し、連想メモリや近似検索に適したチップであることを実証したという。