技術分野の採択率33%、最多採択はベルギーimecの11件

2023年6月に京都で開催される「2023 Symposium on Technology and Circuits」のデバイス・プロセス技術分野には、ここ10年で最多の273件の応募があり89件が採択され、採択率は33%だった。このほか、Late News(一般応募締め切り後に緊急性の高い論文受付)に9件の応募があったが採択されなかった。

国・地域別応募件数で50件を上回る応募したのは中国と韓国だったが、採択件数ランキングは、韓国20件、台湾16件、米国15件、欧州13件、次いで日本とシンガポール各10件だった。中国は5件にとどまった。投稿論文のうち大学からの応募が158件(全体の58%)、企業(独立研究機関を含む)からの発表は115件(同42%)だった。

採択論文の機関別発表論文件数ランキングは、ベルギーimecが11件でトップ、次いで国立シンガポール大学が10件、Samsung Electronicsが8件、国立台湾大学およびTSMCが5件ずつ、KAISTの4件と続いており、シンガポール大学の活躍が目を引く。日本勢の最多が2件で、東京大学、産業総合研究所、キオクシア、ソニーの4機関。Rapidusと協業するというIBMは、招待講演には登壇するものの一般応募の採択件数は1件と寂しい状態である。

デバイス・プロセス分野の注目論文10件を主催者が公開

VLSIシンポジウム委員会は、デバイス・プロセス技術分野の注目論文を10件公開した。このうち先端CMOSデバイス技術および先端メモリプロセス技術に関する論文は2件ずつとなっている。

先端CMOS:SamsungがGAA 3nmプラットフォームを発表

- World’s First GAA 3nm Foundry platform Technology (SF3) with Novel Multi-Bridge-Channel-FET (MBCFETTM) Process (論文番号:T1-2)

Samsung Electronicsは、4nm FinFETプラットフォームに比べ、22%の速度向上と34%の電力向上、0.79倍の論理面積削減を実現する世界初のGAA(Gate-All-Around) 3nmファウンドリプラットフォーム技術(同社における呼称「SF3」)を発表する。

FanFETからGAAトランジスタ・アーキテクチャへの移行に関する技術詳細が報告される予定。このSF3テクノロジは、同社の量産型GAA(SF3E)のアップグレード版である。GAAの同社の呼称であるマルチブリッジチャンネルFET(MBCFET)のユニークなプロセス設計により、SF3は一定のスタンダードセルの高さで同等の性能を持つさまざまなナノシート幅を提供し、チップレベルの電力-性能マトリックスをFinFETプラットフォームよりも強化したという。

-

図2 (左)今回開発されたGAA SF3とFinFET SF4の性能/消費電力/面積の比較。(右)開発されたMBCFETTMの断面図および固有プロセス最適化のポイント (出所:VLSIシンポジウム2023 委員会、以下すべて)

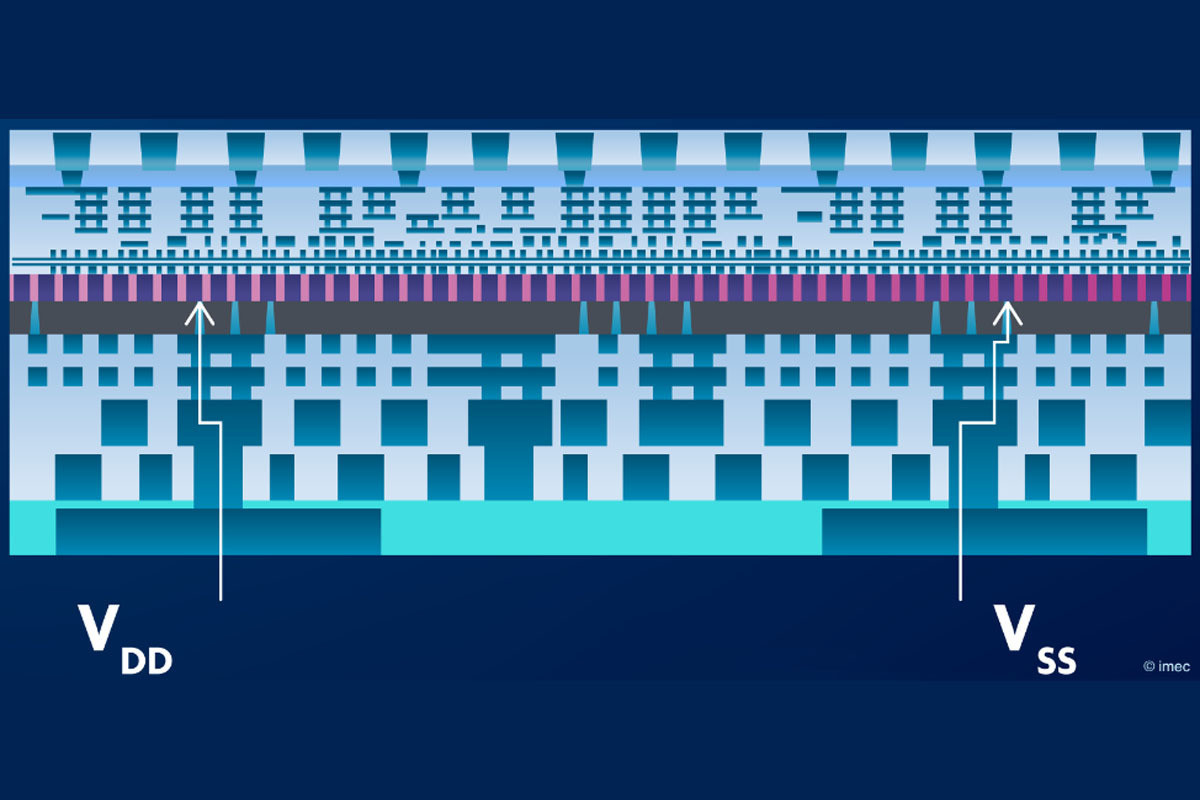

先端CMOS:imecがゲートピッチ48nmのモノリシックCFETを開発

- Nanosheet-based Complementary Field-Effect Transistors (CFETs) at 48nm Gate Pitch, and Middle Dielectric Isolation to Enable CFET Inner Spacer Formation and Multi-Vt Patterning (論文番号:T1-3)

究極のCMOS FETアーキテクチャといわれるCFETを開発中のimecは、ゲートピッチ48nmのモノリシックCFETを開発したことを発表する予定。モノリシックCFETの製造プロセスはボトム側トランジスタのチャネルとゲート電極、トップ側トランジスタのチャネルとゲート電極を積層するものとなるが、縦方向のボトム側トランジスタ(PFET)とトップ側トランジスタ(NFET)のスペースは30nmである。モノリシックCFETのサブスレッショルド・スウィングはNFETが70mV/dec.、PFETは75mV/dec.と良好な特性を得たという。またインナースペーサーの形成、マルチVtを可能にするミドル・ダイエレクトリック・アイソレーションを導入することによって特性を改善したともしている。

先端メモリプロセス:キオクシアとWDが超高層3D NAND向け新技術を披露

- Highly Scalable Metal Induced Lateral Crystallization (MILC) Techniques for Vertical Si Channel in Ultra-High (> 300Layers) 3D Flash Memory (論文番号:T7-1)

キオクシアとWestern Digital(WD)は共同で、300層を超える3D NAND向けに金属誘起横方向結晶化(MILC)技術の実証についての発表を行う予定。垂直のメモリホール内に形成した14μmのマカロニ型シリコンチャネルにおいて、MILCを用いたチャネルの単結晶化を実現できたという。新たに開発したNiのゲッタリング技術によって、セル信頼性を劣化させることなく、40%以上の読み出しノイズの低減と、10倍のチャネルコンダクタンスを実現したとする。

メモリ:SK hynixが3D強誘電型NANDで4値セル動作を実現

- QLC Programmable 3D Ferroelectric NAND Flash Memory by Memory Window Expansion Using Cell Stack Engineering (論文番号:T7-2)

SK hynixは、独自の3D窒化物チャージトラップ型(CTN)NANDを用いて、世界初となる3D強誘電型NAND(Fe-NAND)で4値セル(QLC)動作を実現したことを報告する予定。同社はFe-NANDの上層インターレイヤとHfO2ベースの強誘電層の複数の組み合わせで最適化を図り、4値セル(QLC)の隣接しきい値Vth分布の最低ギャップマージンが0.24Vであることを確認。これらにより、メモリウィンドウ最大10.5Vを確保し、4値セルプログラム可能な3D Fe-NANDを実現したとしている。