AI/マシンラーニング向けデバイス分野の注目論文

AIおよびマシーンラーニング向けデバイス分野では以下の論文が注目論文として紹介された。

14nmプロセスでPCMを使ったDNNハードウェア実装(論文番号(T13-3) T0077)

“Fully on-chip MAC at 14nm enabled by accurate row-wise programming of PCM-based weights and parallel vector-transport in duration-format”, P. Narayanan et al., IBM

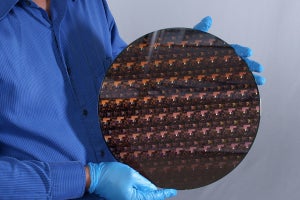

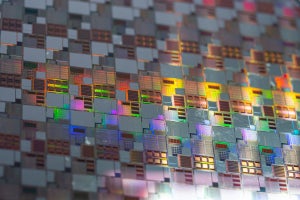

IBM Researchは、14nmプロセス技術で試作したクロスバー型相変化メモリ(PCM)のテストチップについて報告する。

このチップではPCMはアナログ抵抗素子(ARES)として用いられ、クロスバー型PCMアレイのタイルが複数配列されてメッシュを形成し、各タイルは512×512の重み係数行列を表現し並列積和演算を行っている。深層ニューラルネットワーク(DNN)内の活性化信号は二次元メッシュ上を、パルス幅変調方式でタイルからデジタルデータのI/Oを担うLanding Pad(LP)まで伝搬する。誤差を3%未満に抑える正確な重み係数の書き込みのため行ごとの書き込み方式を採用し、4つのPCMデバイスにアナログの重み係数を効率的に書き込む。

このARESチップを用いてソフトウェア実装とほぼ同じ認識精度をもつ2つのDNNのハードウェア実装を行い、1つ目はARESチップ内で信号がタイル間伝搬する2層のネットワークによる画像認識、2つ目はARESチップとオフチップの活性化関数回路を組み合わせた再帰型長短期メモリ(LSTM)ネットワークによる誤差信号の伝搬に対する安定性を確認したという。

3Dヘテロジニアス集積、非シリコン基板分野の注目論文

3Dヘテロジニアス集積、非シリコン基板/材料およびデバイス分野では以下の3件の注目論文に選ばれた。

高移動度In2O3酸化物トランジスタ技術(論文番号 (T2-4) T0011)

“First Demonstration of Atomic-Layer-Deposited BEOL-Compatible In2O3 3D Fin Transistors and Integrated Circuits: High Mobility of 113 cm2/V⋅ s, Maximum Drain Current of 2.5 mA/μm and Maximum Voltage Gain of 38 V/V in In2O3 Inverter”, Mengwei Si et al, Purdue University

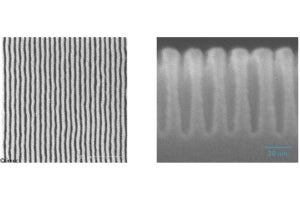

Purdue大学が、初めて実現されたBEOL工程に適用可能かつALDで成膜されたIn2O3チャネルを備えた3D Fin構造トランジスタとその集積回路について報告を行う。

まずIn2O3チャネル平面構造トランジスタにおいて、チャネル膜厚制御ならびに成膜後のアニール技術により113cm2/V の高いチャネル移動度と、2.5mA/μmの高いドレイン電流を実現したとする。また、ALD In2O3を用いて、最小駆動電圧(VDD)0.5V、最大電圧ゲイン38V/Vのゼロゲートバイアス印加インバータを実現したという。

またALDの均一な成膜特性を用いて、3D Fin構造トランジスタも実現したともしており、これらの成果により、ALDで成膜した酸化物半導体デバイスが優れた性能を持ち、BEOL工程に適用可能な3次元一体形成型集積回路を実現するための有望な技術である事が示される模様である。

積層型CMOSイメージセンサに適用可能な混載STT-MRAM (論文番号 (T2-5) T0142)

“3D stacked CIS compatible 40nm embedded STT-MRAM for buffer memory”, M. Oka et al., Sony Semiconductor

ソニーは、積層型CMOSイメージセンサに適用可能な40nm embedded STT-MRAM(Spin-Torque-Transfer Magnetic Random Access Memory)について発表する。

CoFeBベースの縦型磁気トンネルジャンクション(p-MTJ)の最適化により、ウェハ積層プロセスによって引き起こされる磁気特性の劣化を抑制することに成功したという。また、プロセス改善により、-30℃における40ns以下の高速書き込み、105℃における1010回以上の書き換え耐性、そして85℃における1秒以上のデータ保持を達成したともする。

さらに、embedded MRAM(eMRAM)の用途拡大のため、不揮発性メモリとeMRAMを同一チップに混載する融合技術も提案するとのことで、これら融合技術により、データ保持時間1秒〜10年以上が1チップで達成されるとしている。

n-TSVと裏面配線技術で実現するロジック向け裏面電源ネットワーク技術(論文番号(JFS2-6) T0046)

“Enabling Logic with Backside Connectivity via n-TSVs and its Potential as a Scaling Booster”, A.Veloso et al., imec

imecは、低温(LT)でのウェハ・ウェハ(W2W)接合の後、極端なウェハ薄化(STI酸化膜下のSi厚さを370nmから20nmまで薄化)と、ウェハ厚さに連動したさまざまな高さのW充填ナノTSV(n-TSV)によって可能になった裏面接続のSiチャネルFinFET(Lgate>20nm、フィンピッチ45nm)を報告する予定である。

この方式は、信号と電源のネットワークを分離することを目的として、電源ネットワークをウェハ裏面に移動することで、IRドロップの低減が期待できるという。また、3Dプロセスがデバイスの特性に与える影響を詳細に評価した結果、(1)nmosの移動度と駆動電流の向上(最大15%)、(2)pmosの駆動電流ロスの減少(〜3〜10%)と大きなRext、(3)ΔVT〜130mVは、最後に追加のアニールを行うことで回復可能であり、ばらつきとマッチングを厳密に制御可能などの知見が得られたとする。

また、BTIの劣化は見られず、最終アニールの選択が静電容量や信頼性の向上に有効であることもわかったとしている。

メモリ分野の注目論文

メモリ分野では、以下の2件が注目論文に選ばれた。

SSTアシストを使ったSOT-MTJの動作実証(論文番号 (T11-3) T0071)

“First Demonstration of Interface-Enhanced SAF Enabling 400oC-Robust 42 nm p-SOT-MTJ Cells with STT-Assisted Field-Free Switching and Composite Channels”, Ya-Jui Tsou et al., TSRI

台湾半導体研究センターは、CMOSコンパチブルで400℃の耐熱性を持つ42nmサイズの垂直スピン軌道トルク磁気トンネル接合(p-SOT-MTJ)デバイスについて報告を行う予定。

界面特性を改善した合成反強磁性層(SAF)と改善されたイオンビームエッチング(IBE)技術により、初めて130%というトンネル磁気抵抗比(TMR)を実現したという。

これまで報告された中では最も高い440℃という耐熱性を持つSAFになるとのことで、SAF磁界とコバルト(Co)/白金(Pt)の多層レイヤ(ML)とリファレンス層との磁気結合は、磁気結合された面心立方方位構造(fcc)の組織構造を持つ多層膜(MCFTM)バッファーにより強化されている。

また、TaN/WとTa/Wの組み合わせからなるSOTチャネルはβ-Wの厚さ限界(<~5nm)を打ち破り、MTJのエッチングウィンドウを拡大するほか、TaN/Wチャネルは〜-0.27 という大きな実効スピンホール角度を示すという。さらに、スピン注入トルク(STT)アシストにより、外部補助磁界なしで確定的なSOT書き込みが実現されたともしている。

強誘電体HfZrOの書換疲労とリカバリーの評価(論文番号(T6-3) T0052)

“Characterization of Fatigue and Its Recovery Behavior in Ferroelectric HfZrO”, TSMC, P.J.Liao et al.,

TSMCは、さまざまな電界ストレス下でのSILC(ストレス誘起リーク電流)測定に基づいた、HfZrO強誘電体キャパシタの分極疲労の調査結果について報告する。

高電界ストレス下では分極の発現とSILCの増加には強い相関関係があり、これはHfZrO膜中で酸素空孔の再分布や上下電極間でのpercolation path(浸透経路)の形成に起因し、特に高周波サイクル時に生ずるという。

一方、低電界ストレス下での分極疲労はSILCを増加させることなく発生しており、これはP-E loop(分極-電界の履歴曲線)測定やTEM/PED(プリセッション電子回折)による材料分析により、電荷トラッピングが主な要因であることが明らかになったという。

発表では、低電界ストレスで発生する分極疲労を高電界ストレスの短周期サイクルを定期的に入れ込むことで電荷トラッピングや酸素空孔のコントロールにより効果的に回復させ、室温で分極による書換耐性をSILC劣化なしで、1012回以上に改善した結果を紹介する予定だという。