記者説明会では、VLSI Technologyシンポジウムで発表される一般採択講演81件の中から特に注目される発表論文11件の概要が紹介された。

先端CMOS分野の注目論文

先端CMOS技術分野では、4件の注目論文が選ばれた。

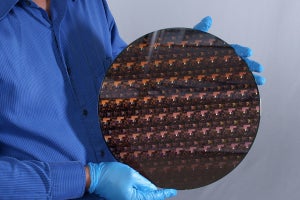

「フォークシート構造のN/Pトランジスタ技術」(論文番号 (T2-1)T0030)

“Forksheet FETs for Advanced CMOS Scaling: Forksheet-Nanosheet Co-Integration and Dual Work Function Metal Gates at 17nm N-P Space”, H. Mertens et al., imec

imecは、ゲートオールアラウンド・ナノシートを利用したフォークシート構造のN/Pトランジスタの集積結果を報告する。フォークシート型トランジスタで、ナノシート型と同等のゲート長22nmまで短チャネル効果が抑制できることを確認できたという(サブスレッショルドスイング66〜68mV/dev)。

また、チャネル形成後のウェットクリーニングを最適化することにより、ゲート界面のトラップ形成を抑制し、トランジスタのオン・オフ特性を改善したとする。さらにフォークシート構造を用いることで、従来構造によるスケーリングの難点であるDual work function metal gatesの間隔を17nmまで縮小することに成功したともしている。

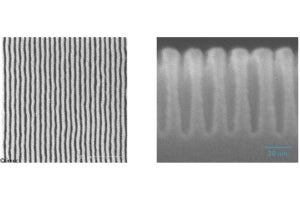

「2D材料チャネルMOSFET技術」(論文番号 (T2-3) T0035)

“Advancing Monolayer 2D NMOS and PMOS Transistor Integration From Growth to van der Waals Interface Engineering for Ultimate CMOS Scaling”, C. J. Dorow et al., Intel

Intelは、2D材料チャネルがMOSFETトランジスタの究極のスケーリングを可能にし、ムーアの法則に基づく半導体微細化を今後数十年にわたって可能にすることを示す研究成果を報告する。

厚さ1nm以下の単層TMD(Transition Metal Dichalcogenide)チャネルを用いて、CVD法、MBE法、シード成長などで製造したnおよびp-MOSFETの動作実証をした。新しいコンタクトメタルを用い、MBE法で形成したMoS2チャネルNMOSデバイスは、ばらつきが少なく、既報では低いコンタクト抵抗(Rc)0.4kΩ・μm、小さいヒステリシス、77mV/decの良好なサブスレッショルドスロープ(SS)値を得た。CVD法で形成したWSe2チャネルPMOSデバイスではCVD膜を用いた素子として最も良好なSS値89mV/decが得られた。一方、オン電流はNMOS に及ばないことも分かった。転写が不要な選択成長WS2膜を用いたトランジスタでは、シード成長を用いたWS2チャネルを用いたものとして最高クラスのオン電流10μA/μmを達成したという。

積層GeSiナノシート・ナノワイヤートランジスタ(論文番号(T15-2) T0039)

“First Highly Stacked Ge0.95Si0.05 nGAAFETs with Record ION = 110 μA (4100 μA/μm) at VOV=VDS=0.5V and High Gm,max = 340 μS (13000 μS/μm) at VDS=0.5V by Wet Etching”, Yi-Chun Liu et al., 国立台湾大学

国立台湾大学の研究チームは、8層Ge0.75Si0.25ナノシート構造と、7層Ge0.95Si0.05ナノワイヤー構造をH2O2ウェットエッチングで実現したとする。

8層Ge0.75Si0.25は高いチャネル間均一性を示した。L4 valleyにおける小さな輸送有効質量(mt)と大きな状態密度有効質量(mDOS)、そして低いRS/D/Rtotalによる、7層Ge0.95Si0.05の高い性能を実証したという。VOV=VDS=0.5V において一層あたりION=110μA(チャネルフットプリントあたり4100μA/μm)のレコードと、VDS=0.5Vでの高いGm,max=340μS(13000μS/μm)がGe/GeSi 3D nFETsで得られたという。

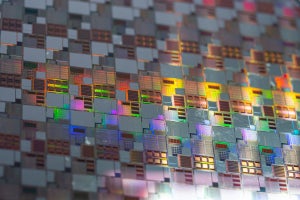

二種金属配合のダマシン配線技術(論文番号 (T5-2) T0107)

Dual Damascene BEOL Extendibility With Cu Reflow / Selective TaN And Co/Cu Composite”, P.Bhosale et al., IBM Research

IBM Researchは、デュアルダマシン(DD)を用いた配線接続工程の集積化が28nmピッチ以下まで微細化できることを報告する。

2つの新しいプロセスフローとして、(1)信頼性を損なうことなくビア抵抗を低減できるようにTaNバリア膜の選択成膜を適用したCu系ダマシン接続技術、(2)微細配線と幅広配線の性能向上のために金属材料技術を駆使した革新的な二種金属配線構造(dual metallization scheme)技術を開発したという。これらのプロセス技術上の革新によって、ビア、信号線および電力線の抵抗を改善したほか、ハイ・パフォーマンス・コンピューティング(HPC)用途では、高アスペクト比の電源レールに二種金属配線(dual metallurgy)を用いることで最高クラスの性能を提供するとしている。

量子コンピューティング分野の注目論文

量子コンピューティング分野では、1件の注目論文が公開された。

シリコン量子ビット向け埋め込み型微小磁性体の集積(論文番号 (JFS5-5) T0150)

“Buried nanomagnet realizing high-speed/low-variability silicon spin qubits: implementable in error correctable large-scale quantum computers”, S. Iizuka et al., AIST

産業技術総合研究所は、埋め込み型電源配線技術に着想を得て、高速かつ低ばらつきなシリコンスピン量子ビット動作を実現する埋め込み型微小磁石の集積方法を提案するという。

スピン量子ビットの極近傍に埋め込まれた微小磁石が生み出す大きな傾斜磁場により、高速な量子ゲート操作を実現し、かつ、自己整合製造プロセスを用いることで傾斜磁場のばらつきに起因する量子ゲート操作の忠実度ばらつきを抑制したとする。

TCADに基づくシミュレーションを実施し、先行研究と比較して約10倍速いラビ振動(高速スピン反転)と、一定のプロセスのばらつきの条件下で99%以上の忠実度を実現可能であることがわかったとのことで、同手法は、2次元格子配置を用いた誤り訂正可能な大規模集積量子コンピュータに実装可能であり、シリコンを用いた実用的な大規模集積量子コンピュータへの道を切り開くものと期待されるとしている。

(次回に続く)