VLSIシンポジウム 2024におけるプロセス・デバイス技術分野(従来のVLSI Technology Symposium)の採択論文数は95件。そのうち、今回はVLSIシンポジウム委員会が厳選したメモリ分野の注目論文4件を紹介する。

高集積NVDRAMの積層可能なポリシリコンチャネル4F2トランジスタをMicronが発表

- 4F2 Stackable Polysilicon Channel Access Device for Ultra-Dense NVDRAM(論文番号:T16-2)

Micron Technologyは、32GビットNVDRAMに積層可能な4F2 Poly-Si TFTの最適化を報告する。熱処理プロセスの制限に対応したチャネルのポリシリコンの結晶化とソース・ドレインの活性化のためレーザーアニールを適用することで、低温成膜によるゲート酸化膜では10年相当の信頼性を確認したとするほか、デバイス特性は上層プロセスの影響を受けにくく、特性は上層と下層の間でよく一致したという。

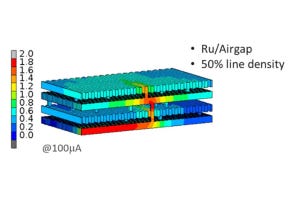

ワード線エアギャップとチャージトラップ層を分断する3D NANDプロセスをMicronが発表

- A Confined Storage Nitride 3D-NAND Cell with WL Airgap for Cell-to-Cell Interference Reduction and Improved Program Performances(論文番号:T1-3)

またMicronは、3D NANDの革新的なプロセスフローを考案し、ワード線エアギャップとチャージトラップ層の分断を実現したことも報告する。エアギャップがワード線間の寄生容量を低減し、書き込み時間改善を可能にしたとするほか、チャージトラップ層の分断により隣接セル間干渉の改善、および横方向拡散による電荷ロス抑制を実現。これらにより積層膜厚のさらなるスケーリング(薄膜化)が可能になるとするほか、チャージトラップ層の分断による書き込み消去ウィンドウの劣化は、膜厚最適化により改善できることをTCADにより示したという。

ハーフピッチ16nmで集積されたCXL向け大容量セレクタオンリーメモリ技術をSK hynixが発表

- First Demonstration of Fully Integrated 16nm Half-Pitch Selector Only Memory (SOM) for Emerging CXL Memory(論文番号:T1-5)

SK hynixは、セレクタオンリーメモリ(SOM)のスイッチング特性のメカニズムを解明したことを報告する。このメカニズムをTCADシミュレーションに組み込むことで、コア回路設計と書き込み/読み取りスキームに基づいた先進的な材料・プロセス開発が可能となり、Compute Express Link(CXL)メモリ向け16nmハーフピッチSOMの開発に成功したとする。また、750mVの読み取りウィンドウマージンと製品レベルのRaw Bit Error Rate(RBER:訂正回路で誤り訂正する前の不正ビット数)を達成するとともに、200ppmのRBERの条件下において、リードディスターブ、高温リテンション特性(>10年@125℃)といった信頼性も確認したとする。

十分なリテンション特性を有するHZO系材料を用いた不揮発性SRAMをソニーなどが発表

- HZO-based Nonvolatile SRAM Array with 100% Bit Recall Yield and Sufficient Retention Time at 85°C(論文番号:T2-1)

ソニーセミコンダクタソリューションズは、フラウンホーファー研究機構および独NaMLabと共同で、厚さ10nm以下のHfZrOx(HZO)を含む金属/強誘電体/金属キャパシタを用いた16kビット規模の不揮発性SRAMアレイを試作したことを報告する。

この強誘電キャパシタの製造プロセスは過去に報告されたFeRAMと同じものであり、同一チップ上に不揮発性SRAMとFeRAMを形成。ロバストなデータ復帰シーケンスを用いることで、一連の不揮発データ保存、供給電源の切断、データ復帰動作を完全に実行し、測定温度85℃において電源切断200秒後でも100%のビットリコール動作を実現したという。この結果は、HZO系材料を用いた不揮発性SRAMとFeRAMのハイブリットメモリシステムによって、エッジコンピューティングの低消費電力化が可能となることを示唆するものとなるという。