プロセス・デバイス技術分野で最多採択は韓国の24件

VLSIシンポジウム 2024におけるプロセス・デバイス技術分野(従来のVLSI Technology Symposium)の応募件数は355件。採択件数は94件で採択率24%。地域・国別で見ると、韓国が24件で最多、次いで中国の22件、欧州14件、台湾および日本の10件、シンガポール5件と続いている。発表機関別では、Samsung Electronicsが前回の8件から倍増の16件でトップ。2位はimecの10件で3位は韓KAISTならびに国立シンガポール大学の各5件と続いている。日本勢で複数採択されたのは東京大学の3件、キオクシアならびにソニーセミコンダクタソリューションズの各2件の3機関。ちなみにRapidusに技術提供を行っているIBMは2件(昨年はゼロ)となっている。

全94件の一般講演の中で、特に注目されるのは以下の9件だろう。

- 3nmプラットフォーム(Intel)

- 最小ゲートピッチ48nmの3D CFET向け裏面コンタクト技術(Samsung)

- 2nm以降の裏面電源供給技術(IBM)、

- MoS2チャネルを用いたスケーリングトランジスタ(TSMC)

- ワード線エアギャップとチャージトラップ層を分断する3D NAND(Micron)

- 4F2高密度32GビットNVDRAM(Micron)

- ハーフピッチ16nmで集積されたCXL向け大容量セレクターオンメモリ(SK hynix)

- 極薄In2O3と厚膜In2O3ゲート電極で構成される全酸化物材料トランジスタ(Purdue Univ./Samsung)

- 熱影響を考慮したオングストローム世代のPPA性能評価(imec)

以下、VLSIシンポジウム委員会が厳選したデバイス・プロセス分野の注目論文を紹介したい。

先端CMOSロジック分野の注目論文

先端CMOS:IntelがIntel 3トランジスタ技術を発表

- An Intel 3 Advanced FinFETPlatform Technology for High Performance Computing and SOC Product Applications(論文番号:T1-1)

IntelはFinFETプロセスを最適化し、Intel 4に比べて面積を10%縮小しつつ、トランジスタの性能改善、配線プロセス最適化、設計・製造協調最適化により15%の性能向上と信頼性改善を果たしたIntel 3プラットフォームを発表する。

先端CMOS:Samsungが3次元積層トランジスタ技術を発表

- Highly Manufacturable Self-Aligned Direct Backside Contact (SA-DBC) and Backside Gate Contact (BGC) for 3-Dimensional Stacked FET at 48nm Gate Pitch(論文番号:T1-2)

Samsung Electronicsは、自己整合ダイレクト裏面コンタクトおよび裏面ゲートコンタクトを備えた3次元積層トランジスタを発表する。同技術はゲートピッチ48nm を実現したもので、完全な3次元積層製造フローによるN/Pトランジスタのしきい値電圧調整、垂直共通コンタクトによるN/P接続といった3次元積層トランジスタに必要な技術の確立に成功したとしており、これにより1nm以下のスケーリングが可能になるという。

先端CMOS:IBM/Samsungが共同で2nm以降のナノシートトランジスタ向け裏面電源供給を発表

- Backside Power Distribution for Nanosheet Technologies Beyond 2nm(論文番号:TFS2-3)

IBMと研究パートナーであるSamsungは、裏面電源供給ネットワーク技術をナノシートトランジスタに適用するためのさまざまなアプローチを検討した結果を発表する。深掘りビア方式では、移動表面ビア裏面電源線方式以外では、セルレベルの微細化に利点は無く、ビア抵抗がボトルネックとなり得る一方で、直接裏面コンタクト方式は、最適な微細化を実現することを確認したとしており、結果として、裏面コンタクト形成時の合わせズレに対する耐性を有する新しい自己整合裏面コンタクト方式をナノシートトランジスタに適用することで良好なデバイス特性と信頼性を実証したという。

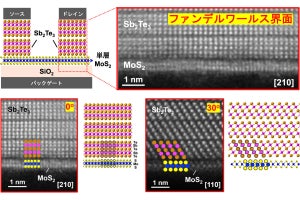

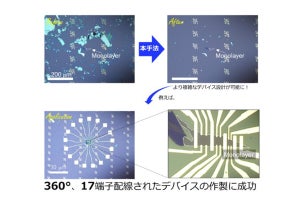

先端CMOS:TSMC/台湾国立陽明交通大がMoS2チャネル材料によるトランジスタスケーリング技術を発表

- On the Extreme Scaling of Transistors with Monolayer MoS2Channel(論文番号:T1-4)

TSMCと台湾国立陽明交通大学は、スケーリングに有望な2D遷移金属ダイカルコゲナイド(TMD)材料において、チャネル長とコンタクト長の両方のスケーリングを実証したことを発表する。コンタクト抵抗をコンタクト長11nmまで低く抑えながら、チャネル長のスケーリングは少なくとも12nmまでIONを増加できることを確認したほか、チャネル長19nmでSbベースの金属コンタクトを持つMoS2トランジスタでは1130mA/mm(VDS=1V)の電流密度と190Ω・mmの低コンタクト抵抗を電気特性として確認したという。