2020年6月15日~18日(米国時間)にかけて開催された「2020 Symposium on Technology and Circuits(VLSIシンポジウム2020)」ではさまざまな技術や回路に関する発表があったが、今回は5G向けデバイスとフォトニクスデバイスの両分野から、東京工業大学/NEC、Samsung Electronics、Qualcomm/Samsung、IBMによる注目論文を紹介したい。

偏波MIMO対応28GHz帯トランシーバーを発表した東工大/NEC

5Gではフェーズドアレイによるミリ波無線通信を行うが、伝送速度向上のため、1つのアンテナから2つの直交する偏波信号を送受信する偏波MIMOに対応することが求められている。東京工業大学(東工大)とNECのグループからは、CMOS技術で作成した5G向28GHz帯フェーズドアレイ無線機が発表された。

16個のCMOSチップを搭載し、64アンテナ素子のフェーズドアレイを用いて偏波MIMOによるミリ波無線通信を実証したという。従来問題になっていた偏波間の信号漏洩をICに内蔵したリークキャンセル回路により補正することで、変調精度(EVM)を7.6%から3.2%に改善することに成功したとしている。

5G対応マルチスタンダード無線機を開発したSamsung

Samsung Electronicsは、14nm FinFET CMOSで製造した5G向けマルチスタンダード無線機を発表した。

0.575から5.925GHzの周波数帯における2G/3G/4G/5Gのすべてに対応しており、受信機は、9つの信号系統を持ち、7バンドのキャリアアグリゲーションかつ、4×4MIMOに対応している。また、送信機は、2つの信号系統を持ち、こちらもキャリアアグリゲーションに対応しているほか、別途、2バンド対応のGNSS受信機も内蔵している。これらの無線フロントエンドとベースバンドICとの間をデジタルインタフェースとすることで、大幅な配線本数の削減に成功したとしている。

7nm EUVを活用した5G/AI統合SoCをQualcommとSamsungが開発

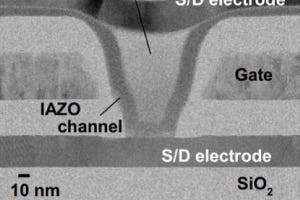

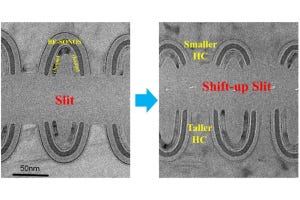

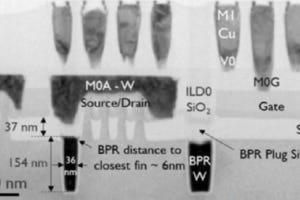

米国のモバイル通信半導体サプライヤであるQualcommは、ファウンドリ事業を手掛ける韓Samsung Electronicsと共同で、5Gプラットフォームである「Snapdragon 765」の概要と7nm EUVプロセスを用いた技術の発表を行った。

Snapdragon 765は、前世代の8nm FinFETプロセスに比べ、20%の性能改善および35%の消費電力削減を実現したという。これらは、性能・電力の最適化を可能にする素子分離技術(MDB:Mixed Diffusion Break)やDual-CPP(ゲートピッチ)を基盤とした、設計と製造技術の最適化(DTCO)により達成された。これらにより、ロジック・メモリの動作電圧を下げることに成功し、世界規模で高品質な技術を提供する5GとAIの統合が可能になったという。

シリコンフォトニクス技術を活用した8×8光スイッチをIBMが開発

IBMはシリコンフォトニクス技術を活用し、8光入力8光出力のネットワークスイッチ・チップを開発したことを報告した。同チップには、光信号パスを切り替える制御回路も実装されている。

光信号パスの切り替え時間は15ナノ秒以下と高速であるほか、従来のパケットベースの電気スイッチと異なり、光/電気変換機能も不要なため、低消費電力で動作するという。90nm SOI CMOSテクノロジーを使用して試作され、チップサイズは12mm×7mm、消費電力は1.5Wだという。

3次元集積シリコンフォトニクスで実現する光学サンプリングADコンバータ

高周波入力信号に対する従来のA/Dコンバータ(ADC)の精度は主にサンプリングクロックのジッターによって制限されていた。UC Berkeley、MIT、LBNL、CNSEの研究グループは26fs rms以下という低ジッターの光パルスを使用して入力信号をサンプリングするADCを実装することによりこの問題に対処したことを報告した。

2チャンネルADCの試作品はTOV(Through-Oxide Via)と呼ばれる銅を用いたTSVにより接続された65nm CMOSとシリコンフォトニクスの3D統合プラットフォームで実現したとする。また、250ps(実効サンプリングレート:4GS/s)というパルス間隔の光パルスを用いることにより、このADCはDC付近でのSNDR:40dB、45GHzの入力に対しては37dBという高性能を実現している。