「2020 Symposium on Technology and Circuits(VLSIシンポジウム2020)」では、FinFETやGate-All-Around(GAA)のチャネルに、従来のSiにかえてキャリア移動度の高いGeやSiGeを用いた次世代デバイスに関するオンデマンドセッション「GeおよびSiGeデバイス」が開催された。同セッションでは、シンガポール、ベルギー、台湾、ドイツ、米国から合計5件の発表が行われ、Ge系デバイスについて世界中で検討されていることがうかがえた。

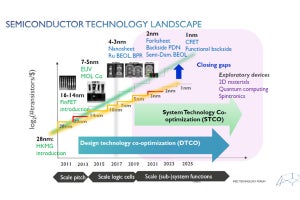

非Siチャネルの採用はいつから?

一方、先端CMOSに関するライブセッションでは、「非Si(Ge、SiGe、III-V族)チャネルのデバイスが生産に導入されるのはいつ頃になるか?」という問いが、オンライン越しに視聴者に投げかけられた。結果は以下の通りで、約半数の回答が「5nm未満の第3世代以降から」で、非Siチャネルの登場はだいぶ先になりそうだ。

- 5nm未満の第1世代から:10.3%

- 5nm未満の第2世代から:25.6%

- 5nm未満の第3世代以降:47.4%

- 決して導入されない:16.7%

以下に、非Si材料・デバイスと3次元集積技術分野で、前評判の高かった注目論文を3件紹介する。Intel、キオクシア、およびTSMCの発表である。

モノリシック三次元集積化技術で実現されるGaNとSiトランジスタ

Intelは、GaNトランジスタが形成された300mmのSi(111)基板上にSi FinFETをモノリシック集積化することで、同社のGaNとSiデバイスのヘテロジニアス集積化技術を大きく進展させたことを報告した。

同技術により、Si FinFETはウェハトランスファされたSi(100)結晶層に特性を劣化させることなく形成することができたという。さらに、以下のGaNトランジスタ技術のイノベーションを実現した。

- ドレイン電流が1.8mA/μmのエンハンスメント型・デプレッション型GaNトランジスタ

- 28GHzで20dBmの高い出力飽和電力と57%のピーク電力負荷効率(PAE)を有するショットキーゲート型GaNトランジスタ

- 高性能・低リークなカスケード・マルチゲート型GaNトランジスタ

- ESD保護向けの超低COFFなGaNショットキーダイオード

これらのGaNデバイスがすべて300mm Si(111)基板上に集積させることに成功したという。

高温耐性を有する酸化物半導体In-Al-Zn-Oチャネルトランジスタ

キオクシアの研究チームは、CMOSバックエンドプロセスとの整合性が高い新規酸化物半導体In-Al-Zn-Oをチャネル材料に用いた、ゲート長40nmのサラウンディング・ゲート縦型トランジスタの動作実証に世界で初めて成功したことを報告した。

作製した縦型トランジスタは従来の酸化物半導体In-Ga-Zn-Oをチャネルに用いたトランジスタに比べて高いスケーラビリティを示しながら、熱安定性(~420℃)と高移動度(12.7cm2/Vs)を両立しているという。

さらに、フローティングボディ効果のないこの縦型トランジスタは1011回を超えるエンデュランス特性と優れた信頼性を示したとしている。

この研究結果は3D-LSI向け高性能BEOLトランジスタの実現に向け、新たな道を切り開くことが期待されると研究チームでは説明している。

高帯域幅メモリ(HBM)向け低温チップ接合・積層技術

TSMCの研究チームは、12-high(12-Hi)および16-high(16-Hi)の高帯域幅メモリ(HBM)を実現するための低温接合と積層技術を発表した。

最下層のロジックダイから最上層のDRAMに至る電気的結合を構築しバンド幅と電力消費を調査した結果、SoIC技術を用いた12-Hiおよび16-Hi構造は、マイクロバンプ技術と比較してそれぞれ18%および20%のバンド幅の改善を示しながら、それぞれ8%および15%の電力消費の改善も示したという。

また研究チームは、HBMの熱特性、および将来の高バンド幅HBMに向けて、ピン密度の増加のためのボンディング間隔とTSV寄生容量の低減のためのダイ厚さのスケーラビリティについても報告した。