「2020 Symposia on Technology and Circuits」(以下、日本での通称であるVLSIシンポジウムと略記)は、オープニングとなる基調講演セッションから始まった。

4件のバーチャル基調講演のうち2件が日本人による講演であったが、最初の登壇は米Analog Devicesのプレシジョンテクノロジー&プラットフォームグループのバイスプレジデントであるJen Lloyd氏が「シリコンデバイスは環境により優しく:持続可能性のために回路の革新が必要な理由」と題した講演を行った。

同氏は「持続可能な開発は、人類が直面する大きな課題の1つであり、短期的な課題は、炭素排出の削減である。半導体産業は、教育から農業に至るまで経済のあらゆるセクターを変革した情報通信革命を生み出した。半導体産業における技術革新は持続可能性問題解決のための鍵を握っている」とし、半導体の性能向上やチップ面積縮小によるシリコン消費量の削減など具体例を上げながら話した。

次にNTTドコモ執行役員の中村武宏氏が「5Gの発展、そして6Gへ」と題し、1Gから2020年代の5Gに至るモバイル通信の流れ、そして2030年代に予想される次世代6Gへの展望を述べた。

Intelが語った次世代コンピューティングに必要なLSIの再構築

6月17日(米国時間)の基調講演セッション・パート2では、まず最初に米Intelの最高技術責任者(CTO)であるMichael C. Mayberry氏(図1)が「コンピューティングの未来:データトランスフォメーションがどのようにVLSIを再構築するか?」と題して講演を行った。

伝統的なコンピューティングの性能向上は半導体デバイスのスケーリング(比例縮小)に依存してきた。その実現のために、デバイス構造や材料を工夫してきたわけだが、これからの半導体コンピューティングで重要なのは、半導体デバイスのスケーリングだけではなく、へテロジニアスプロセッサの集積化や、システム・回路・技術の同時最適化、ソフトウェアドリブンなハードウェア、AI(人工知能)、優れたコンピュータロジックだとMayberry氏は指摘した。

これまでのサーバーやパソコンだけではなく、クルマや、テレビを中心とするブロードキャスティングサービス、監視カメラ、IoTデバイスなどさまざまなデバイスから生み出される非構造化データ(unstructured data)がますます増えるため、これらの技術が欠かせなくなるという。

さらに、あふれるデータを整理するために、データセンターのトポロジーが変わり、これまでの中央集権的なデータセンターから分散的なデータセンターに変わっていく。結果として、データを転送するコストはコンピュータコストを超えるようになる。つまり、クラウドベースのデータセンターからローカルのデータセンター、通信基地局内でのクラウドWANやエッジ基地局でのデータセンター、さらにはエッジでのデータセンターなどへと分散していくとする(図1)。

データセンターが分散化され、非構造化データが整理されてもデータの量そのものは増え続け、データ量は3年で倍増すると同氏は予測している。

ムーアの法則はまだまだ続く

分散型データセンターの時代になれば、そこに搭載される半導体チップは、CPUとGPU、DSP、NPU(ニューラルネットワークプロセッサ)などxPU(多数の異種プロセッサで、ヘテロプロセッサと呼ばれる事がある)になる。これを実現するヘテロプロセッサアーキテクチャは、命令セットがプロセッサごとにあり、極めて複雑になる。集積度が増すだけではなく、プログラミングも複雑になり、開発期間が長期にわたるようになる。メモリ容量も膨大になり、消費電力も膨大になる。加えてAIチップは特に学習チップの集積度が増加することで、より複雑化する。こうした結果、まさしくコンピューティングギャップが生まれてしまうと同氏は指摘する。

その解決策の1つがモジュラー方式だという。コンピューティングをレイヤごとに抽象化し、新たな自動化ツールを活用していく。ハードウェア的には3次元化や2.5次元化によって機能ごとに集積していくことにより、ムーアの法則が継続していくことになるとする。

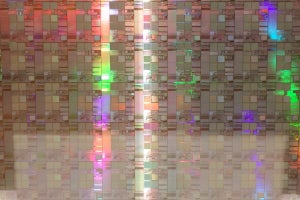

高集積化技術として、トランジスタはFinFET構造からナノワイヤFETやナノリボンFETと呼ばれる積層GAA(Gate All Around、チャネルをゲートで完全に取り囲む)構造になり、さらには2次元材料を用いたトランジスタの研究も進んでいる。また、パターンニングはウェハ面内バラつきを抑えるためにポリマーの化学的特性を利用してパターンの規則性を制御するセルフアライン技術であるDSA(Directed Self-Assembly:自己組織化)技術の採用が期待されているという。

さらに、3次元積層については、メモリとロジックとの3次元積層がすでに実用化しており、Intelはすでに2~2.5DのEMIB(Embeded Multi-die Interconnect Bridge)技術や、3次元のFoveros技術、これらを合わせたCo-EMIB技術を商品化しているとする。最近出荷が始まったSoC「Lakefield」はFoveros技術を採用したものである。加えて、IntelのFPGAはチップレットやHBM(High Bandwidth Memory)モジュールを2.5Dパッケージに入れたり、3次元のLakefieldと組み合わせたりするようなハイテクパッケージの時代となるともした。

そして、「この先、ハードウェアとソフトウェアの共同進化が必要になる。従来のフォンノイマン型コンピューティングからディープラーニング、さらにビッグデータの解析に必要なグラフ解析、人間の頭脳の仕組みを模倣するニューロモーフィック、そして最終的には従来のコンピュータでは解けなかった問題を解く量子コンピューティングへと向かうだろうが、それは2030年以降になるだろう」とMichael C. Mayberry氏は述べた。

最後にMayberry氏は「(1)非構造化データを意味のある情報へと転換する作業が次世代コンピューティングを牽引する。(2)ムーアの法則は、伝統的なスケーリングだけではなく、システム・設計・プロセスの同時最適化と3次元積層によって今後も続く。(3)現在も将来もLSIの課題は山積みで、取り組むべきテーマはまだまだたくさんある」という3つをまとめとして語り、話を結んだ。