8月に開催された「Intel TECHtour. MY」の初日に公開されたのは、ペナン・キャンパス(図1、2)のPG7/PG8と呼ばれる2つの建物で構成されたPGAT(PenanG Assembly & Test)と呼ばれる組立/検査施設と、パッケージング技術開発や製品のバリデーション(動作確認)開発のための「デザイン・開発ラボ(Design and Development Labs)」の2つの施設である。

ちなみにいずれの場所も、写真撮影や携帯電話、筆記用具などの持ち込みは禁止であるので、以下に掲載する写真は断りのない限りIntelから提供されたものとなる。

アセンブリ・テスト工程

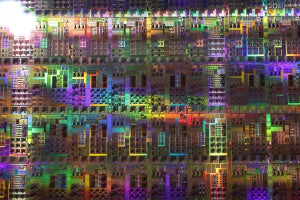

ここでのアセンブリ・テスト工程は、タイル(チップレット)を基板に接着し、その上にヒートスプレッダを装着して、各種テストを行う工程で(図3)、2日目に見学するクリム・キャンパスからテープに封入された形でペナン・キャンパスに納品されてきた検査済みダイをテープから取り出し、有機樹脂基板に取り付ける。その後、ダイがストレスを受けてもサブ基板から外れないように強力な接着材であるエポキシ樹脂を注入し、ダイの周辺もエポキシ樹脂で固める作業が行われる(図4、5、6)。その後、ヒートスプレッドを装着して、物理的な意味では製品の完成となる。

パッケージの処理を終えた後はテスト工程である。温度と電圧の負荷をかけることにより初期不良を事前に低減させるためのバーンインテストが行われる。その後、様々な電気的なテストを行ない、チップとしての機能に問題がないかをテストする。最後に、マザーボードなどに実際に装着して、エンドユーザーが使う環境を想定したテストを行なう。これについては改めて後ほど説明する。

Design & Development Labsが公開

ペナン・キャンパスには、主にパッケージ関連の開発や動作検証(バリデーション)などの開発を行なっている「Design & Development Labs」がある。同研究所に所属する社員しか入室できないとされ、退室の際には金属探知機による身体検査が行われるほど厳格な管理が行われていた。今回はその一部が報道関係者に公開された。

Intel デザイン・エンジニアリンググループ VP 兼 マレーシアデザインセンター 所長のSursh Kumar Perabala(スレッシュ・クマル・ペラバラ)氏によると、同ラボの機能は「Eコア・IP動作検証」、「製造歩留り向上のためのデザイン・テスト協業」、「ポスト・シリコン動作検証」、「電気的動作検証」、「電力・性能動作検証」、「アーリーカスタマー・エンゲージメント」の6つだという。以下にそれぞれを簡単に説明する。

Eコア・IP動作検証

現在のIntelのCPUには、Pコア(高性能コア)とEコア(高効率コア)という2つの種類のコアが用意されているが、そのうち、Eコア・IP動作検証は、マレーシアのデザイン&開発ラボが担当している。

製造歩留り向上のためのデザイン・テスト協業

チップ製造時の歩留まりを上げるために、どのような設計をすると歩留りが上がるかを検討。テスト中に発見された改善点は、設計チームや製造チームにフィードバックされ、次のフォトマスク作成に反映される。

ポスト・シリコン動作検証

メモリ、ストレージ、GPUなどの周辺デバイスや拡張カードなどを装着し、実際に動かしてみて問題がないかを確認する。

電気的動作検証

CPUでサポートされている機能が、問題なくスペック通りに動作しているかどうかをオシロスコープなどの機器を使いながらアナログ的に確認する。

電力・性能動作検証

定格のスペックやそれより高い電力やクロックで期待通りの性能が出ているか確認する。

アーリーカスタマー・エンゲージメント

新しいCPUには新しいマザーボードが必要になるが、できるだけ早くそれぞれの顧客向けの検証システムを作り顧客に提供する。

なお、前述したように、ペナン・キャンパスでは、Meteor Lakeはじめ今後ますます増加する3D ICの先進パッケージング(図11)に備えて新施設(コードネーム:Pelican)の工事が進められていた。