SOT-MRAMの課題の主な改善手順

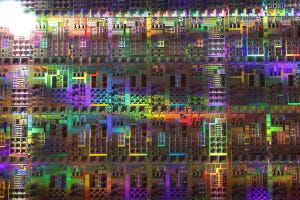

これまでのところ、個々の課題のそれぞれに対するソリューションが成功裏に実証されている。そのいくつかは、imecによって開発され、300mmウェハで実証されている。

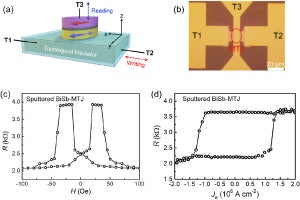

外部磁場の役割は、SOT層の形成に使用されるハードマスクに強磁性体を埋め込むことで実現でき、これにより外部磁場が不要になる。強磁性体は、磁気トンネル接合(MTJ)の自由層に小さな均一な面内磁場を誘導する。2019年にimecは、SOT-MRAMデバイスのサブns書き込みを維持しながら、この「フィールドフリー」スイッチングアプローチが信頼できることを示した。

高書き込み電流に関連する問題は、電圧ゲート(VG)支援アプローチを採用することで部分的に軽減できる。このようなVG-SOT-MRAMデバイスでは、SOT効果が再び自由層のスイッチングに関与し、実際のスイッチングには面内電流を使用する。しかし、電圧制御磁気異方性(VCMA)ゲートは、(トンネル障壁を横切って)電界を発生させてエネルギー障壁を下げることにより、その動作を支援するため、書き込み動作に必要な電流が少なくて済み、動的消費電力が改善される。

VG支援アプローチのさらなる利点は、マルチピラー/マルチビットデバイス構造への扉が開かれることである。1つのMTJピラーをSOTトラックに接続する代わりに、4つ(またはそれ以上)のMTJピラーを共有SOTトラックの上に実装できるようになった。このマルチピラー、マルチビットデバイス内で、個々のピラー(またはビット)は、そのVCMA(Voltage-Controlled Magnetic Anisotropy)ゲートに電圧を印加することによって選択できる。これにより、エネルギー障壁が減少し、スイッチングが容易になる。また、共有SOTトラックを介して書き込むには、(4つではなく)1つのアクセストランジスタのみが必要である。これにより、ビットセル全体がよりコンパクトになる。

しかし、これまでのところ、マルチピラー操作と完全に互換性のあるフィールドフリーソリューションは実証されてはいない。たとえば、上に示したように、フィールドフリースイッチングのソリューションでは、p-MTJピラーのそれぞれに強磁性体を埋め込む必要があり、スケーラビリティが大きく損なわれてしまう。

フィールドフリー、ゲート電圧アシストSOT-MRAMマルチピラー構成

imecは、IEDM 2022にて、これらのすべての課題に一度に対処する、完全に機能する新しいマルチピラーSOT-MRAMデバイスのデモを行った。

-

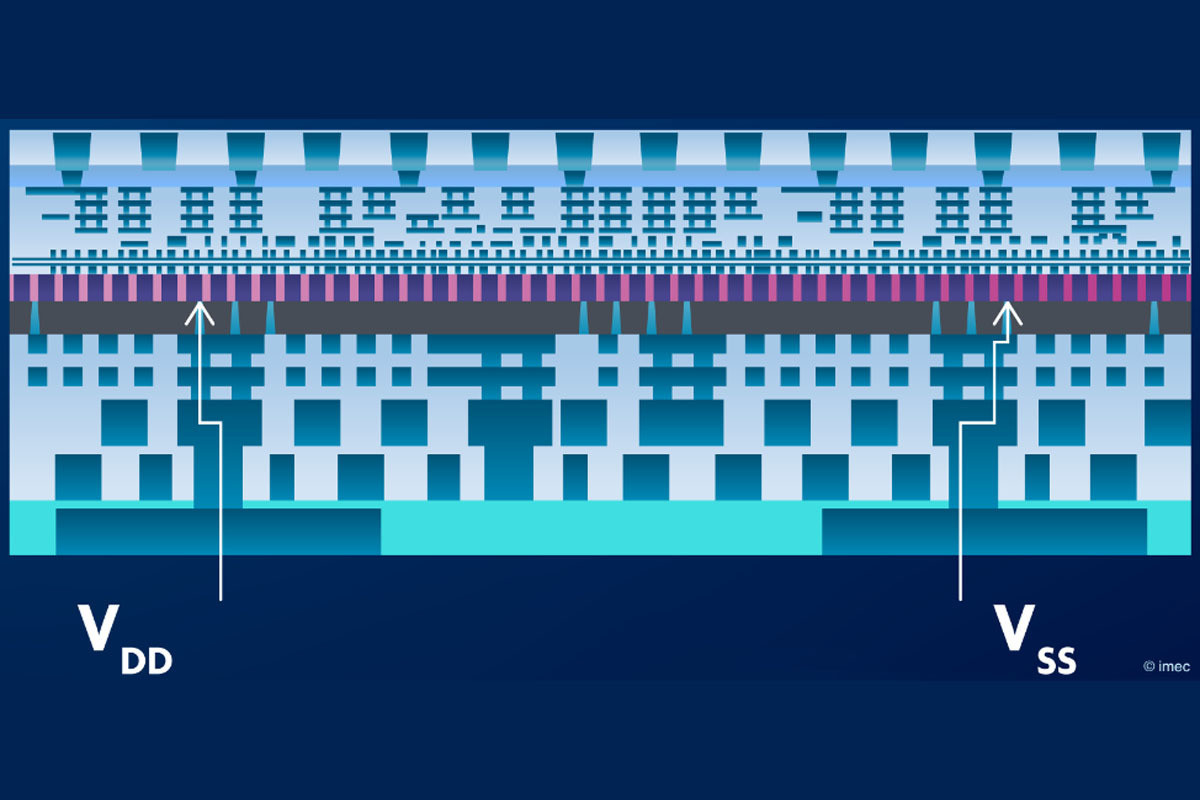

図2 電圧制御VCMA効果とマルチピラーデバイスの概略図。(a)ゲート電圧は、スイッチングのエネルギー障壁を変調する。(b)ハイブリッドSOTトラックは、マルチピラーデバイスでのフィールドフリー操作を可能にしている

このデバイスは、ハイブリッドスピンソースと呼ばれる共通のSOTトラック内に面内磁性層を実装することにより、スケーラブルで無磁場のソリューションを実装する。この共通の面内磁気層は、個々のメモリ要素に結合する。これは、各ピラーの磁場のように機能するが、個々のMTJスタックの一部ではなくなり、スケーラビリティが向上する。

第2に、VCMA効果は、実際のスイッチングのエネルギー障壁を変調して低下させることにより、書き込み操作を支援し、スイッチング エネルギーを低下させる。

-

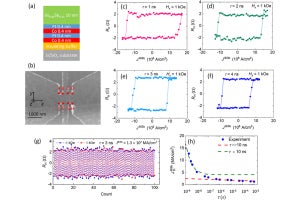

図3 参考文献およびフィールドフリーデバイスでの1ns でのエネルギー消費を示すベンチマークプロット。ハイブリッド SOTトラックを備えたデバイスは、参照サンプルに匹敵する高いSOT効率を示している (参考文献:[1] K. Garello et al., IEEE Symp. on VLSI Circuit, 81-82 (2018);、[2] K. Garello et al., IEEE Symp. on VLSI Technology, 194-195 (2019);、[3] H. Honjo et al., IEEE IEDM 28.5.1-28.5.4 (2019);、[4] M.Y. Song et al., IEEE Symp on VLSI Technology, 377-378 (2022) (as shown at 2022 IEDM))

そして第3に、このVCMA支援のコンセプトにより、ビットごとに必要なトランジスタの数が減り、面積の消費とスケーラビリティが向上する。

このデバイスアプローチにより、高いスイッチング効率(60fJ/ビットの消費電力)、高速な動作速度(最低300ps)、および1012を超える耐久性を備えた無電界スイッチングが可能になる。300mmの統合テクノロジは、1ピラーおよびマルチビットSOTデバイスの両方に適しており、CMOSおよびBEOLと互換性がある。

産業導入に向けた取り組み

新規の不揮発性SOT-MRAMデバイスは、上述した特徴により、高密度のラストレベル組み込みキャッシュアプリケーションの魅力的な代替手段となりうるレベルに近づいた。

この不揮発性SOT-MRAMメモリを市場に投入するには、さらにいくつかの開発が必要である。現在の研究では、SOTトラックとMTJピラースタックの両方の設計を改善することにより、スイッチングエネルギーをさらに下げることに重点が置かれている。さらに、imecの研究チームは、SOT-MRAMデバイスのアレイ構成に取り組んでおり、その技術を工業化に向けて進めている。

また、SOT-MRAMメモリが別個のオフチップキャッシュダイの一部になり、ダイとダイまたはダイとウェハのボンディング技術を使用してロジックおよび/または下位レベルのキャッシュメモリに結合されることも概念的に想像できよう(3DスタックSRAMキャッシュダイを備えたAMDの3D V-Cacheテクノロジに対応している)。このオフチップソリューションは、個別のダイで個別に最適化され、従来のラストレベルの組み込みキャッシュ実装よりもコスト効率が高くなることが約束されている。

|

|

Sebastien Couet

2008年に独ハンブルグ大学で物理学の博士号を取得後、2009年から2014年までベルギーKatholieke Universiteit Leuven(KUL)で博士研究員を務め、磁性/酸化物ヘテロ構造の界面物理を研究。2014年にimecに入社。現在は磁気に関するプログラムディレクターを務めている。組み込みおよびスタンドアロンアプリケーション向けのさまざまなMRAMベースのメモリコンセプトや、その他の探索的磁気デバイスコンセプトの開発を指揮している。 |

|

|

Gouri Sankar Kar

2002年にインド工科大学で半導体デバイス物理学の博士号を取得後、ノーベル賞受賞者(1985年、量子ホール効果)のクラウス・フォン・クリツィング教授と量子ドットFETについて研究を実施。2006年には、独Infineon/Qimondaにリードインテグレーションエンジニアとして入社。同社にてDRAMアプリケーション用の縦型トランジスタの開発に取り組む。2009年、imecに入社。現在はプログラムディレクターを務めている。スタンドアロンおよび組み込みアプリケーションの両方のSCM、DRAM、およびMRAMプログラムの研究戦略とビジョン立案を担当している。 |