HMCの展示

2012年のSC12でもMicronは、HMCを動作させるデモを行っていたが、1個のHMCをテストボードに載せたもので、いかにも試作品という感じであった。しかし、2013年のC13ではサンプル出荷も始まったこともあり、HMCチップのウェハとHMCを採用した各社のボードを並べて大々的な展示を行っていた。

次の写真の手前はDRAMのウェハで、30nm、4GBと書かれている。このウェハは当然、Micron製と思われる。そして、後ろ側のウェハはIBM製のロジックチップのウェハで、32nmのSOIプロセスと書かれていた。また、IBMのプレスリリースでは、HMCはIBMのTSV技術を使って製造されていると書かれており、Micronのウェハを受け取って、IBMが加工し、自社で製造するロジックLSIと組み合わせてHMCを製造していると考えられる。

展示されていたArira Designのボードは、AlteraのStratix V FPGAのHMC接続の評価用ボードで、Alteraから評価用として提供中とのことである。正式にHMC接続をサポートするのはArria 10 FPGAとなり、早期アクセスプログラムに参加している顧客にはすでに開発ツールが提供され、設計が行われていると述べられている。

Open SiliconのボードはXilinxのVertex-7 FPGAの評価用のボードと思われる。Xilinxは、Virtex-7 FPGAは10Gbpsと12.5GbpsのHMCのトランシーバをサポートすると謳っている。

Pico ComputingはPCI Expressのアドインカードのメーカーで、「EX-800」という製品は、Stratix V FPGAを4個とHMCを1個、そしてボードの外部とのインタフェースのPCI Gen3×16とStartix VへのPCI Gen3×8の4ポートの間を接続するスイッチ(中央下)を搭載したボードで、HMCの4つのリンクをそれぞれのStratix Vに接続している。160GB/sと従来の製品に比べて高メモリバンド幅で、メモリネックにならずにFPGAの並列処理能力が生かせるという製品である。説明パネルの下には小さい字で、Sandia国立研究所が開発費を出したと書いてあった。

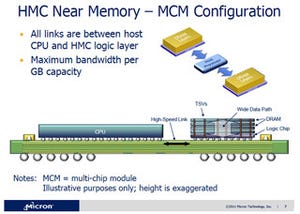

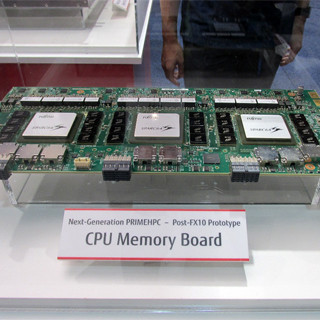

富士通の次期スパコンのプロトタイプボードは、3個のSPARC64 CPUを搭載し、それぞれのCPUの両側に各4個のHMCを付けている。実装密度を高めるため、これらのHMCは小型のパッケージのものを使っており、2リンクを並列にしてCPUチップに接続していると考えられる。ボード全体では48リンクあり、仮に10Gbpsでの転送としても、1.92TB/sのメモリバンド幅となる。

HMCはサンプル出荷の段階であり、まだ、本格的な製品と呼べるボードは無いが、SC13での展示は、HMCのポテンシャルとユーザ側の期待を感じさせるものであった。