RISC-V ISAの実用性

細かい点で改良を積み重ねたコマーシャルISAに比べて、アカデミックなISAは、シンプルであるが実用性が低いと思われているが、少なくともRISC-Vは高い実用性を持っていることを以下に示す。

次の2つのグラフは、SPECint2006のコードサイズを比較したものである。左のグラフは32bitアドレス、右のグラフは64bitアドレスの場合である。32bitアドレスの場合は、コード圧縮を行うRV32Cを基準の100%にとり、RV32、x86、Armv7-A、Thumb-2、MIPS32、MIPS16eのコードサイズを比較している。Thumb-2が101%でRV32Cとほぼ同じコードサイズであるが、RV32や他のISAでは126%~140%のサイズで、MIPS32は173%とかなり大きい。一方、64bitアドレスの場合は、RV64は141%、Armv8は129%、x86-64は131%となっている。つまり、圧縮を行うRV32CやRV64Cのコードサイズはx86やArmより小さい。

一方、圧縮を行わないRV32やRV64は競合ISAと比較すると若干コードサイズが大きめである。

-

SPECint2006のコードサイズの比較。圧縮RISC-Vのコードサイズを100%として正規化を行ったグラフである。左は32ビットアドレス、右は64ビットアドレスのコードの比較である。どちらのケースも圧縮したRISC-Vのコードサイズが一番小さい

前のコードサイズは命令メモリに必要な静的なサイズの比較であるが、次の図は、実行に当たってメモリから読まれたメモリ量を比較したものである。左端から400.perfbenchを始めとする12のベンチマークプログラムのグラフが並び、右端は12プログラムの幾何平均である。

各プログラムの5本の棒グラフは、左からx86-64、Armv7、Armv8、RV64G、RV64GC ISAの読み込みバイト数を示している。幾何平均で見ると、一番、読み込みが少ないのがRV64GCで、x86-64がそれに次ぐ。この傾向は、どのプログラムでもおおむね同じである。一方、圧縮を行わないRV64GではArmv7よりは多少、メモリフェッチは少ないが、Armv8やx86-64よりは多いという状況である。

つまり、静的命令サイズでも動的メモリフェッチ量でもRISC-Vは他のISAより優れているが、それは命令圧縮の貢献が大きく、圧縮を使わない場合は、他のISAと似たレベルか若干、悪めという感じである。

次の図は、SPECintベンチマークプログラムの実行に当たって実行された命令数を比較したものであり、12プログラムの幾何平均だけを示している。棒グラフは左から、x86-64 Micro-ops、x86-64、ia32、Armv7、Armv8、Armv8 micro-ops、RV64G、RV64GC macro-opsを示している。RV64GC macro-opsの1.09はx86-64の1.0やArmv8の1.06より実行命令数は多少多いが、まあ、競争にならないという値ではない。簡単なアーキテクチャを活かしてクロックを上げられれば、性能的には逆転が可能な圏内である。

命令圧縮の貢献が大きいが、命令のフットプリントのサイズは、他の競合命令アーキテクチャと比較しても小さく優れている。一方、実行命令数でみると、ベストではないが、まあまあ、のところである。つまり、RISC-Vは他の商用ISAと比べてそん色ないと言える。

RISC-Vをめぐる世の中の動向

最近、NVIDIAが、将来のGPUに内蔵する組み込みコントローラはRISC-Vに切り替えることを公表した。また、Western DigitalもHDDやSSDコントローラなどに内蔵するマイクロコントローラはRISC-Vに切り替え、年間1B(10億)コアを使用すると公表した。

もし、Western Digitalが1コアあたり1.00ドルをロイヤリティとして払っているとすると、無料のRISC-Vに切り替えることで10億ドルの節約になる。ただし、ソフトバンクの買収前の2015年末のArmの年間売上高は約10億ドルであり、Western Digitalが払っているロイヤリティは1.00ドルより大幅に安いか、Arm以外の自社開発のコアも数多く使っているのではないかと思われる。

しかし、どちらであろうと、相当数のRISC-Vの需要が生まれることになり、ハードIPや開発ツールななどが増えるのはRISC-Vコミュニティにとっては望ましいことである。

なお、この講演では触れられなかったが、カリフォルニア大学バークレイ校のRISC-V開発者達が作ったSiFiveという会社がある。Kreste Asanović教授はSiFiveのチーフアーキテクトでもある。

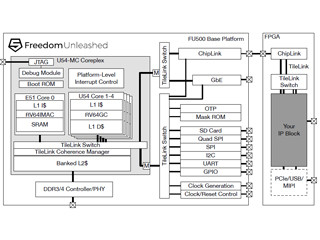

SoCを作る場合には、CPUはRISC-Vで安上がりにできるとしても、その他にGPUやDSPなどのプロセサや、DRAMコントローラ、PCI Express、USBなど多くのIPが必要になる。これらを自前で開発するのは大変であるので、一般にはIPを販売している会社から買ってくることになる。しかし、ライセンス料はかなり高く、これがSoCを作る上で大きな参入障壁になっている。

これに対してSiFiveは、IPベンダと交渉し、初期ライセンス費用を安く抑えて、製品が売れたら、売り上げからライセンス費用の割引分を回収していくという仕組みを作っている。このような仕組みがあれば、お金がないスタートアップでもSoCの開発を行うことができ、産業界でのRISC-Vの採用を推進する力になっている。

そして、RISC-Vは学術的な研究で用いられる標準的なISAになりつつある。コンピュータアーキテクチャ関係ではトップ学会の1つ「MICRO」の50回目となるMICRO-50(2017年開催)ではRISC-Vのワークショップが最も多くの出席者を集めたという。

さらに、RISC-Vの本も出版されてきて、大学のコンピュータアーキテクチャ教育にRISC-Vが使われるケースが急速に広がっているとのことである。

研究、教育、産業界という改革サイクルをうまく回して、オープンなエコシステムを確立していきたいとKreste Asanović教授は語っていた。