今後2~5年でパターニングに影響を与える開発分野は何か?

EUVLの革新に加えて、3次元構造をますます利用するロジックとメモリ双方の新たなデバイスコンセプトの台頭から、独自のパターニングの機会が生まれている。

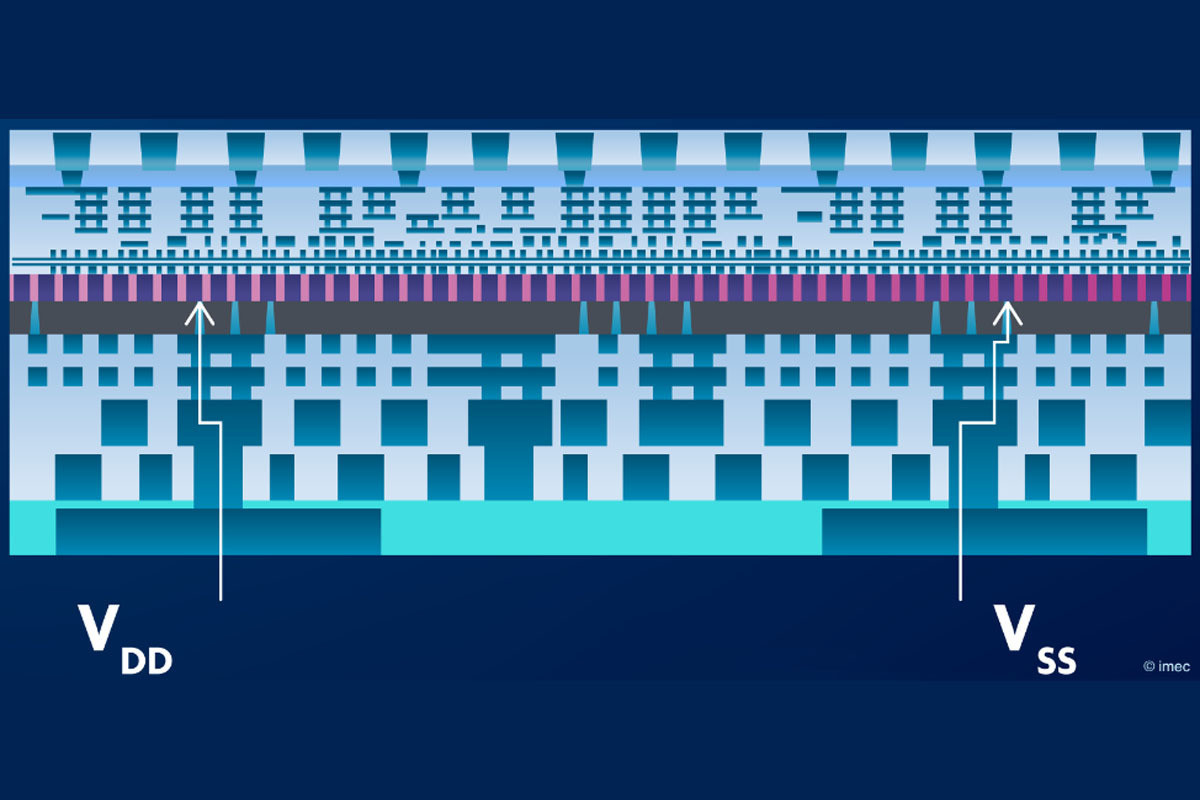

相補型FET(complimentary FET:CFET)は、Gate-All-Around(GAA)ナノシートを超えた将来のデバイスアーキテクチャであり、1つのFETチャネルを別のFETデバイスの上に積み重ねるという概念を利用している。デバイスの製造には、アクティブ部分、ゲート、ソース/ドレインの凹部、およびMOL(Middle of Line:FEOLとBEOLをつなぐ工程)の第0層配線であるM0Aのコンタクト形成を実現するために、高アスペクト比のパターニング手順が必要である。その上、金属や絶縁膜などの大量の材料によるリセスが不可欠である。ボトムアップ堆積や領域選択堆積(Area Selective Deposition:ASD)などのイノベーションは、CFETのプロセスの複雑さを軽減する上で重要な役割を果たす可能性がある。

また、5トラックから4トラックへのCFETベースの標準セルのスケーリングを可能にするために、CFETデバイスはバックサイドパワーデリバリ(BPD:裏面から電源供給する構造)と統合される可能性があります。この新しいルーティングスキームには、高アスペクト比の開口部と、ゲートスペーサに対する良好な選択性を備えたセルフアラインパターニングが必要となっている。

メモリ領域では、DRAMは現在、ビットセルとして細くて背の高いキャパシタに依存している。密度を高めるためにピッチを縮小すると、キャパシタの横方向のクリティカルディメンション(CD)が縮小し続けるため、容量を一定に保つためにキャパシタの背をさらに高くする必要がある。これは、製造上の問題や歩留まりの低下につながるだけでなく、2D DRAMが基本的な材料の限界に達することも予想される。これらの問題を克服するために、さまざまな3D DRAM構造が検討されており、半導体酸化膜などの新材料を導入する可能性が高く、いくつかの高アスペクト比のエッチングと横方向のリセスステップが必要になる。これらはすべて挑戦的な研究課題である。それに加えて、ライナー、誘電体、および金属による垂直ホールおよび側面キャビティの充填は、今日の3D NANDテクノロジと少なくとも同じくらい困難であると予想される。

imecが挑む持続可能な半導体製造

現在、ICの製造は世界のCO2排出量の約0.1%を占めると推定されている。しかし、プロセスの複雑さが増しているため、 ロジックの製造に関連するCO2排出量は、今後10年間で2倍になると予想されている。同時に、生産されるウェハの総量は、年間約8%増加すると予測されており、このまま何もしなければIC製造に関連するCO2排出量は、今後10年間で4倍になると予想されている。パリ協定によると、すべての産業セクタは、10年ごとに排出量を半分に削減する必要がある。言い換えれば、「何もしない」シナリオでは、私たちの業界は目標の8倍ものCO2を排出することになる。

そのため、持続可能性がimecの研究の重要な柱となっている。imecは、持続可能な半導体技術およびシステム(SSTS)プログラムを開始し、サプライチェーンを集めて、チップ製造の正味ゼロ排出を共同で目標としている。一般的な半導体量産ファブの環境への影響を定量化するために、imec.netzeroと呼ばれる仮想ファブを構築している。開発されたモデルは、機器および材料のサプライヤとのパートナーシップを通じて、継続的にベンチマークおよび検証されている。

先般開催された「SPIE Advanced Lithography and Patterningカンファレンス」にて、高度なIC製造中の炭素排出に対するパターニングの影響の定量的評価を提示した。実際のファブでは、影響の大きい領域が特定され、ソリューションの対象となっている。例としては、フッ素化エッチングガスの使用削減、水の使用削減、希少材料のリサイクル、水素の回収、低線量リソグラフィプロセスなどが挙げられる。

将来のテクノロジーを開発しながら環境への影響に対処することは、困難な作業のように思えるかもしれない。しかし、私たちはそれを行わねばならない。半導体業界はその創造性と革新性で知られているが、環境への影響を減らすためのリソグラフィ・パターニング技術開発にもチャレンジしていく。

|

|

Steven Scheer

2019年にAdvanced Patterning,Process and Materials(APPM)担当VPとしてimecに入社した後、2022年にシニアVPに昇進。責任範囲には、パターニング、ユニットプロセスおよびロジック、メモリ、フォトニクス、3D集積の新材料開発が含まれる。それ以前は東京エレクトロン(TEL)でアカウントテクノロジーディレクターを務め、米ポートランドの顧客を担当していた。TELには13年間勤務し、米国や熊本のTELの工場および東京本社R&D部門でパターニングと洗浄のR&Dを担当していた。研究キャリアは、ニューヨーク州フィッシュキルのIBMにて90/65nmのパターニング開発に取り組んだことからスタートした。テキサス大学オースチン校で化学工学分野の博士号を取得 |