ISC 2015において将来のノードアーキテクチャがどうなるのかというセッションが行われ、NVIDIAのアクセラレーテッドコンピューティング部門のSteve Oberlin CTO、IntelのフェローでデータセンターグループのディレクタのShekhar Borkar氏、ARMのEric van Hensbergen氏の3人が発表を行った。

エクサノードはLOCとTOCの組み合わせ

NVIDIAは、米国の次期スパコン計画でOak Ridge国立研究所に入る予定のSummitスパコンをIBMと共同で開発するメーカーであり、Oberlin氏は、それに使われるVolta GPU開発の中心人物である。

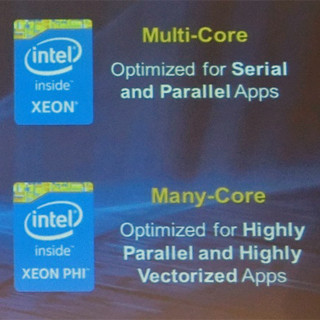

Oberlin氏は、ムーアの法則の衰え、レーテンシ重視とスループット重視、大型ノードと軽量ノード、そしてNICは必要かという4点について、考え方を述べた。

ムーアの法則の衰え

半導体の微細化は、まだ、続いているが、リーク電流の急増から、電源電圧が下げられなくなり、微細化のメリットが少なくなってしまっている。図4.3に示すように昔は、Lを半分にすると、電力は同じで、性能は8倍になった。しかし、今日では電力は4倍になってしまい、それでも性能は2倍にしかならない。

リーク電流が大きくなると、消費電力が大きくなってしまうので、図4.4に示すように、標準スレッショルド電圧(SVt)トランジスタに加えて、低スレッショルド電圧(LVt)と高スレッショルド電圧(HVt)のトランジスタを使うようになってきている。トランジスタのチャネル長を短くすると、Vtが小さくなり、トランジスタの動作時間は速くなるが、リーク電流は大幅に増大する。一方、チャネル長を長くするとVtが高くなり、動作速度は低下するが、リーク電流は大幅に少なくなる。現代のプロセサは、動作時のスピード要求がそれほど厳しくない部分ではHVtトランジスタを使い、一方、どうしてもSVtトランジスタでは遅延時間が大きいというクリティカルな小さな部分に限定してLVtトランジスタを使うというような適材適所の使い分けで、リーク電流の増加を抑えている。