チップレベルからシステムレベルのインタコネクト

現在のハードウェアアーキテクチャは、図4.22のような構成になっている。まず、数10個のコアをキャッシュコヒーレンシを保つチップ上のネットワークで結合したノードを作り、次のレベルとして、複数のノードを搭載するノードボードを作る。ノードボード上の各ノード間は、キャッシュコヒーレンシを維持するオンボードのネットワークで相互接続される。

そして、多数枚のノードボードをキャビネットに収容し、必要に応じて多数のキャビネットを並べる。このとき、ノードボード間の接続はEthernetやInfiniBandが使われ、キャッシュコヒーレンシは維持されていない。

現在のプログラミングモデルは、このシステムアーキテクチャに合わせて作られている。

Extreme-Scaleになると、この構造ではなく図4.23ようになると考えている。ノードは数100~数1000のコアを持ち、そのような多数のコアのキャッシュコヒーレンシを維持するのは負担が大きすぎるので、コヒーレンシを保たないネットワークを使う。ノードボードは複数のノードを搭載し、ノード間でキャッシュコヒーレンシは維持しない。そして、ノードボード間の接続やシステムレベルの接続がキャッシュコヒーレンシを持たないのは現在のハードウェアアーキテクチャと同じである。

同一ノード内のコア間でもキャッシュコヒーレンシが無いというこのハードウェアアーキテクチャをうまく使うためには、プログラミングモデルをこれに合った形に変更することが必要になる。

エクサノードアーキテクチャのたたき台

図4.23を具体化した「Straw-man(藁人形モデル、開発の初期のたたき台のモデル)プロセサ」は図4.24のようになる。

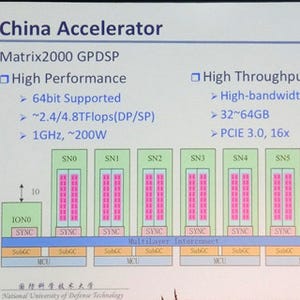

まず、単純なコアを作り、それを多数並べて共通のキャッシュやメモリをアクセスできるブロックを作る。次に、複数のブロックを並べて第2段のキャッシュやメモリをアクセスするクラスタを作る。そして、多数のクラスタを格子状に配置して、2次元メッシュのようなネットワークで接続してプロセサを作る。

5nm世代の半導体プロセスを想定して、プロセサチップは~4096コアを集積し、チップ面積は25mm2、2GHz以上のクロックで動作する。倍精度浮動小数点演算性能は16TFlops以上となり、消費電力は100W以下になる。Flopあたりのエネルギー消費は4-6pJで、プロセサのエネルギー効率は200GFlops/Wを超える。

このプロセサを使うノードは、次の図4.25のようになる。プロセサのパッケージ上に複数の3D積層メモリを搭載し、全体では1TB以上の容量と1TB/sのメモリバンド幅を実現する。そして、DDRxの大容量メモリを接続できるようにして、4TBのメモリを確保する。さらに、他のノードと接続するためのインタコネクトのインタフェースをプロセサチップに内蔵する。

ただし、16TFlopsの演算性能に対して、高バンド幅メモリのバンド幅が1TB/sではちょっと不足ではないかと思われる。特に、この図のようにメモリを16個も搭載するのであれば、1個で250GB/sとしても4TB/sくらいは実現できる。そうなれば0.25B/Flopとメモリバンド幅と演算能力のバランスは、まあまあのレベルになると考えられる。

コアの間を接続するインタコネクトは、第1レベルは共通バスを使う。共通バスは5mm以下の範囲でしか使用できないが、その範囲では1~10fJ/bitと低エネルギー消費のデータ伝送ができる。そして次のレベルでは、マルチポートのメモリ、あるいはクロスバを使う。マルチポートメモリは、1つのメモリに多数のアクセスポートを設け、1つのポートを1つのブロックに対応させる。この接続は1~5mmの範囲で10~100fJ/bitのエネルギー消費でデータ伝送ができる。クロスバはブロック間で任意の接続ができるスイッチを設ける。この方式は2~10mmの範囲で0.1~1pJ/bitのエネルギー消費となる。

その次のチップレベルの接続は、2次元メッシュ接続でパケットスイッチネットワークを使う。5mm以上の距離の接続ができ、多数のクラスタを接続できるスケーラビリティを持つ接続法である。しかし、消費エネルギーは1~3pJ/bitとなる。

多数のプロセサチップを搭載するボードの内部の接続法は明示されていないが、当然、チップ内のメッシュを拡張することはできるし、その他のネットワークでも良い。そして、キャビネット内の複数のボードを集約するスイッチ(一般にTop-of-the-Rackスイッチと呼ぶ)を持たせ、2段のスイッチで接続するFat Treeネットワークでシステムを構成する図となっている。

図4.27はシステムレベルの接続を示すもので、キャビネットから第1段のスイッチ、第1段と第2弾のスイッチ間の接続は光ファイバによるOpticalな伝送を用いるようになっている。

システムの実行効率

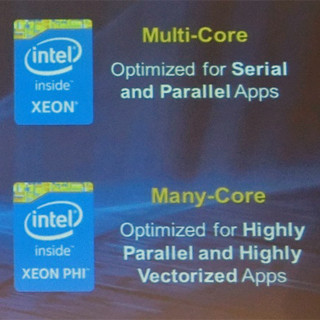

図4.28は、新たに提案されているHPCGベンチマークをワークロードとして実行中のシステムの稼働率を示したもので、青で示されたレーテンシ最適化された大型コアと、緑で示されたスループット最適化されたGPUの処理が交互に発生している。これで見ると、青の破線で示された大型コアの実行効率は平均2.7%、緑の破線で示されたGPUの実行効率は平均1.5%でしかない。一方、緑の折れ線で示されたHPLベンチマークの実行効率は60%から90%を超えており、両者には大きな違いがある。

どうすれば、HPCGのような低効率のプログラムの性能を改善できるかは、まだ、分かっていないが、Borkar氏は、低効率のプログラムの実行効率を高めることが今後の重要な挑戦であると言う。

結論として、Extreme-Scaleの実現のためには、いくつかの分野で挑戦が必要であるが、解決方法は見えてきている。将来のHPCノードは、簡素で効率の高いコア、DRAMやPCMを3D積層してパッケージに搭載する階層的メモリシステム、階層的でヘテロなインタコネクトを使うようになる。

そして、最大の挑戦はシステム効率の改善であると結んだ。