九大の井上教授が用いるアプローチ

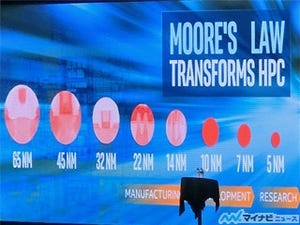

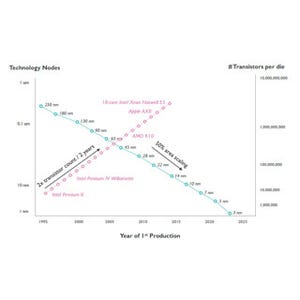

九州大学(九大)の井上先生は、ムーアの法則が止まり、トランジスタの消費する電力が減らなくなると、計算に使われるエネルギーを減らすことがより重要になるという。

従来は、多くの演算を行うことが目的でメニーコア化やGPUの使用が行われ、FPGAによる専用ロジックも使われてきた。しかし、ポストムーアの時代には、More演算ではなく、No More演算を考える必要がある。

例えば、NVRAMの記憶容量の増大を利用して、計算結果を記憶することで再計算を不要にするとか、計算を必要な最低限の精度で行うことにより計算量を減らすとか、ニューラルネットワークによる処理のような処理方法を研究すべきである。

そして、処理を行うデバイスには、メニーコア、GPU、FPGAと言った機能の多様性と同じに作ったつもりでも製造バラつきで特性が変わるという多様性がある。これらの多様性を考慮して、電力を効率的に使うことが重要であるという。

単一ノードで見ても、CPUとDRAMにどれだけの電力を割り当てるかによって処理の実行時間が変ってくる。次の棒グラフは、6本が1組で、左から順に、総電力が140W、130W、…、90Wとなっている。そして1組6本のグラフはCPUとDRAMの電力の比率を変えたものである。そして、計算の対象はA~Eの5種の計算カーネルがあり、それぞれの実行時間をカラーで表わしている。

このように総電力が同じでも、CPUとDRAMへの電力配分によって性能が変わる。また、赤い星で示したTDPに基づく電力配分は、最適な電力配分と比べて、かなり、長い処理時間を必要としている。

次の図は、1Kノードのシステムのデータをプロットしたもので、横軸が正規化した実行時間、縦軸は消費電力である。そして、211.2kW~134.4kWの範囲の5種の消費電力設定でのデータを色分けで示している。

左のグラフはデバイスの特性バラつきを考慮しないで電力配分を行った場合、右のグラフは速めのデバイスは電源電圧を下げて電力を減らし、遅めのデバイスは電圧を上げて高速化するという調整を行った場合である。

総電力を134.4kWにした場合が一番顕著であるが、バラつきを考慮しない場合は一番遅いノードは一番早いノードより64%長い実行時間となっている。一方、性能を一定に近づけるようにデバイスの電源電圧を調整した場合は、遅いノードの実行時間は早いノードの12%増しとバラつきが小さくなり、同一電力でのベンチマークの実行時間で平均1.8倍の性能が得られたという。

なお、この結果は、九大の稲富准教授がSC15で論文発表したもので、井上教授も著者に名を連ねている。

ということで1つのシステムでも、CPUとDRAMの電力予算比率を変える、デバイスのバラつきを考慮してデバイスごとに電力予算を調整することにより、性能/電力を大きく改善できる。

また、井上教授のグループでは、このデバイス多様性を志向した省電力、高性能化技術の開発と、新デバイスとして名古屋大学と協力して単一磁束量子回路、NTT/京大と協力してナノフォトニクスの研究も行っているという。