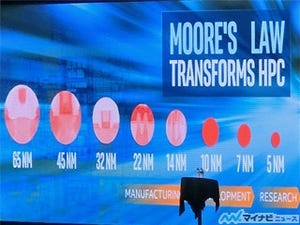

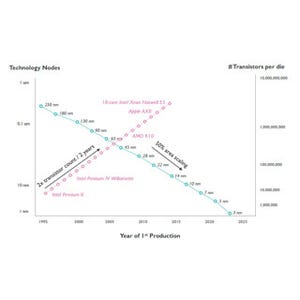

ムーアの法則として知られる半導体の微細化はコンピュータの発展をけん引してきたが、トランジスタの微細化が物理的な限界に近付いており、2025~2030年ころには微細化が止まりムーアの法則が終わってしまうと予測されている。

そうなると、ポストムーアの時代には演算性能(Flops)の伸びは止まってしまう。一方、3次元チップ積層によるメモリバンド幅の拡大や光波長多重(Dense Wavelength Division Multiplexing)通信を使った信号伝送の高バンド幅化(Bytes)は実現の可能性が高く、Flopsではなく、このデータ伝送の高性能化を利用する新たな性能向上の体系を築くことが必要である。そのため、デバイス、アーキテクチャ、システムソフトウェア、アルゴリズム、アプリケーションの各分野の専門家が一堂に会して、ポストムーア時代におけるさまざまな技術的問題について議論しようというのがこのシンポジウムの趣旨である。

|

|

|

ポストムーア シンポジウムの趣旨説明を行う松岡教授 |

シンポジウムの主催者は東工大の松岡聡教授と東大の中島研吾教授で、松岡先生が趣旨説明と、ポストムーアの時代の計算機科学の方向性に関しての意見を述べた。

ITの革新を支えてきたムーアの法則が止まりITシステムの更新が止まることは、社会的危機を引き起こすことになる。ポストムーアにどう対応するかは、デバイス開発の問題だけではなく、情報学全体の英知を結集して取り組むべき問題である。

このシンポジウムは計算機科学、計算科学を融合して解を見つけて行くという取り組みの旗揚げであるという。

松岡先生は、まず、直近の2016年後半に予定している東工大の次世代スパコン「TSUBAME3.0」の概要を説明した。ピーク演算性能は17~18PFlops、メモリ容量は~4PB、ネットワークバンド幅は~1Pbit/sで、これが稼働すれば、京コンピュータを超える日本でトップのスパコンとなる。設置面積は歴代のTSUBAMEと同じ100m2以下で、9~10GFlops/Wという高い性能/電力となるという。

TSUBAME3.0までは良いのであるが、その後のTSUBAME4、5の時代には、リソグラフィの縮小、デナードスケーリングによる性能向上、トランジスタコストの低減は期待できない。このようにムーアの法則が止まることにより、トランジスタあたりの電力は減らず、トランジスタ数に比例して電力が増えてしまうことになる。このような時代に、どのようにして性能向上を継続していくのかというのが問題である。

テクノロジがどのようになって行くのかについて、松岡先生は次のように見ている。トランジスタは速くならないが、メモリの容量やデータ伝送のバンド幅はムーアの法則が止まった以降も増加を続ける。トランジスタ数も増加するが、電力の制限からそれらを同時に動かすことはできない。そのため、用途ごとに最適化したユニットを作り、用途ごとに必要な時だけ電源を入れて使用することになる。

3D積層と低電力の不揮発メモリの使用により、メモリ容量は増加し続ける。データ移動に必要なエネルギーは当初は問題であるが、長距離通信で使われている光波長多重の技術を用いることにより、データ移動のエネルギーの増加は抑えられ一定になる。しかし、レイテンシは依然問題であり、局所性は重要である。このため、増加するメモリ量やバンド幅を有効に利用して性能を改善する汎用的なアルゴリズムを開発することが必要である。

効率の高い専用の処理ユニットの1つの例として、日立製作所が発表したCMOSのIsingチップが挙げられる。このチップは、D-Waveの量子コンピュータと同様の方式で最適化を行う。これで最適化が効率よく実行できれば、トランジスタは有り余るので、このようなユニットをCPUに組み込むことが考えられる。

もう1つの例は、TezzaronのタングステンTSVによる高密度の3Dのチップ積層技術である。通常のTSVは50~100μmピッチであるので、それほど多数の接続はできないが、2μmピッチのTezzaronのTSVなら(50/2)2 = 625とけた違いの本数の接続ができ、バンド幅は本数に比例して増加する。

これらの将来のテクノロジを使ったBytesの伸びをフルに利用するシステムのStrawman(初版の粗い設計)は、次のようなものになる。低電力のCPUがダイスタックの最下層にあり、その上に高速のメモリであるDRAMダイが何枚かスタックされ、さらにその上にNVRAM(不揮発性RAM)のチップがスタックされる。スタック1個でメモリ容量は16TBで、ネットワークとの接続は5~10Tbit/sのバンド幅を持つ。そしてインタポーザで光スイッチと光の入出力機能を集積するチップに接続される。光接続は、多数の波長の信号を1本の光ファイバで送るDWDM(Dense Wavelength Division Multiplexing)を使う。