JSTの戦略的創造研究推進事業ACCELの課題目標

黒田先生の研究は、科学技術振興機構(JST)の戦略的創造研究推進事業「ACCEL」の平成27年度第1期新規課題として採択されており、以下のような目標に挑戦することになる。

黒田先生は、2017年には512GB/sのバンド幅を持つDRAMモジュールを開発してTCI技術を立証する計画である。これは現状のDIMMと比べると32倍のメモリバンド幅であり、TSVを使うものと比べても3倍高速という目標である。

そして、2019年には100GFlops/Wのコンピュータの技術立証を行うという目標を掲げている。この目標はGreen500のトレンドを延長した予測よりも5倍高い目標である。ポストムーアの時代には発熱が制約になるので、電力効率を改善しないとシステムの性能を高めることはできず、電力効率の改善は最重要である。また、電気代の削減やCO2排出削減の点でも電力効率の改善は重要である。

次の図は100GFlops/Wのコンピュータの実装イメージで、フリップチップのサブストレートにSoCチップをマウントするところは普通であるが、SoCの端の部分にDRAMのスタックが重なって置かれており、この部分のTCIでDRAMとSoCは直接通信する。DRAMスタックにはDRAMバスを構成するアクティブなインタポーザがあり、SoCの外側に置かれているDRAMスタックを接続するという構造になっている。

|

|

|

DRAMスタックはTCI+HDSVで作り、アクティブインタポーザに載せる。アクティブインタポーザにはDRAMスタックを接続するDRAMバスが作られている。DRAMとSoCの重なった部分で両者の間の信号はTCIで接続されている |

まとめ

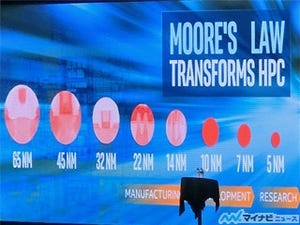

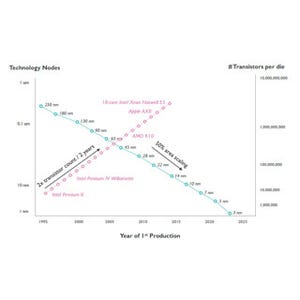

まとめとして、微細化で性能コスト比を改善できなくなるとムーアの法則は止まる。トランジスタコストはEUV露光が実用化されると改善される可能性があるが、発熱はより深刻な問題で、発熱が集積度を制限する。放熱と低電力化技術がシステム性能を決めることになる。

一番有効な低電力化は電源電圧の低減であるが、0.45V程度が下限で、それ以下にするのは難しい。また、理論的な下限は36mVであり、これが実現できたとしても改善の余地は2桁程度しか残っていない。

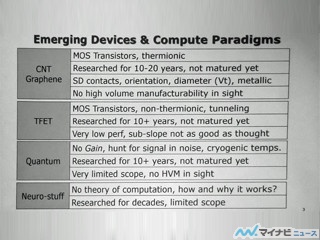

いろいろな研究が行われているが、CMOSに替わる技術の実用化のめどは立っていない。不揮発性メモリは次々とニュースが出るが、大きなR&D投資が続くDRAMとNAND Flashが延命する可能性が高い。

実用化が近いのは3次元集積で、データ伝送距離を短縮し、転送電力を桁違いに削減できる。

黒田先生の提案は、接続を機械式から近接場結合を用いる電子式の接続に代え、この技術を用いてプロセサとメモリを3次元集積するというものである。JSTのACCELの課題では、2017年に512GB/sの8GB積層DRAM、2019年に100GFlops/Wのコンピュータを作る技術の立証を目標としている。